# PhD Thesis

# **Real-Time Software Transactional Memory**

### **António Barros**

CISTER-TR-180504

2018/04/29

### Real-Time Software Transactional Memory

#### António Barros

\*CISTER Research Centre

Polytechnic Institute of Porto (ISEP-IPP)

Rua Dr. António Bernardino de Almeida, 431

4200-072 Porto

Portugal

Tel.: +351.22.8340509, Fax: +351.22.8321159

E-mail: amb@isep.ipp.pt http://www.cister.isep.ipp.pt

### **Abstract**

The current trend in the development of recent real-time embedded systems is driven by (i) a shift from single-core to multi-core platform architectures at the hardware level; (ii) a shift from sequential to parallel programming paradigms at the software level; and finally (iii) the ever increasing demand of new functionalities (e.g. additional tasks with specific timing requirements). These trends taken together increase the complexity of the system as a whole, and have a significant impact on the type of mechanisms that are adopted in order to guarantee both the functional and non-functional correctness of the system. This holds true especially in the case where these mechanisms have to maintain the correctness of data shared between different tasks executing concurrently in parallel.

The access to shared resources (e.g. main memory) on single-core systems has traditionally relied on lock-based mechanisms. At any time instant, a single task is granted an exclusive access to each shared resource. However, assuming the new settings, i.e. multi-core architectures executing a set of potentially parallel tasks sharing data, the big picture changes. Tasks executing in parallel on different cores and sharing the same data may have to compete before completing the execution. It has been proven that lock-based synchronisation approaches, which were sound in single-core context, do not to scale to multi-cores and, furthermore, they hinder the composability of the system, unfortunately.

On the path to solving these issues, Software Transactional Memory (STM) based approaches have been proposed as promising candidates. By using these alternative techniques, the underlying STM service would solve the conflicts between contending tasks while maintaining data consistency, and critical sections would be executed speculatively – i.e. they are executed but if the result of the computation harms the system correctness, then changes made by the computation are reverted and the results are ignored. This way, the details on how to synchronise shared data would be hidden from the programmer, thus representing a significant advantage as compared to lock-based synchronisation techniques regarding the functional correctness of the system. Regarding the non-functional correctness instead, the use of STM based approaches in real-time systems also requires the tasks timing constraints to be met. This is due to the fact that each transaction aborting and repeating multiple times before its eventual commit incurs a timing overhead that might not be negligible and, therefore, must be taken into account to prevent deadline misses at runtime.

This work considers a set of potentially parallel real-time tasks sharing data and executed on a multi-core platform. Assuming this setting, first it proposes a complete framework where an STM service is associated to a set of fully partitioned scheduling algorithms in order to improve the predictability of the system as well as guaranteeing that the timing constraints are met for all the tasks. Then, it proposes the corresponding schedulability analysis for each pair of STM and scheduling algorithms. Finally, it proposes a lightweight syntax to enrich the original Ada programming language in order to support STM for concurrent real-time applications.

# Real-Time Software Transactional Memory

António Manuel de Sousa Barros

Programa Doutoral em Engenharia Electrotécnica e de Computadores

Supervisor: Luís Miguel Rosário da Silva Pinho

### **Real-Time Software Transactional Memory**

### António Manuel de Sousa Barros

Programa Doutoral em Engenharia Electrotécnica e de Computadores

### Approved by:

President: Doutor José Alfredo Ribeiro da Silva Matos

External Referee: Doutor Mario Aldea Rivas External Referee: Doutor Audrey Queudet

External Referee: Doutor Paulo Bacelar Reis Pedreiras Internal Referee: Doutor Luís Miguel Pinho de Almeida

Internal Referee: Doutor Pedro Alexandre Guimarães Lobo Ferreira Souto

Supervisor: Doutor Luís Miguel Rosário da Silva Pinho

May 29, 2018

### **Abstract**

The current trend in the development of recent real-time embedded systems is driven by (i) a shift from single-core to multi-core platform architectures at the hardware level; (ii) a shift from sequential to parallel programming paradigms at the software level; and finally (iii) the ever increasing demand of new functionalities (e.g. additional tasks with specific timing requirements). These trends taken together increase the complexity of the system as a whole, and have a significant impact on the type of mechanisms that are adopted in order to guarantee both the functional and non-functional correctness of the system. This holds true especially in the case where these mechanisms have to maintain the correctness of data shared between different tasks executing concurrently in parallel.

The access to shared resources (e.g. main memory) on single-core systems has traditionally relied on lock-based mechanisms. At any time instant, a single task is granted an exclusive access to each shared resource. However, assuming the new settings, i.e. multi-core architectures executing a set of potentially parallel tasks sharing data, the big picture changes. Tasks executing in parallel on different cores and sharing the same data may have to compete before completing the execution. It has been proven that lock-based synchronisation approaches, which were sound in single-core context, do not to scale to multi-cores and, furthermore, they hinder the composability of the system, unfortunately.

On the path to solving these issues, Software Transactional Memory (STM) based approaches have been proposed as promising candidates. By using these alternative techniques, the underlying STM service would solve the conflicts between contending tasks while maintaining data consistency, and critical sections would be executed speculatively – i.e. they are executed but if the result of the computation harms the system correctness, then changes made by the computation are reverted and the results are ignored. This way, the details on *how* to synchronise shared data would be hidden from the programmer, thus representing a significant advantage as compared to lock-based synchronisation techniques regarding the functional correctness of the system. Regarding the non-functional correctness instead, the use of STM based approaches in real-time systems also requires the tasks timing constraints to be met. This is due to the fact that each transaction aborting and repeating multiple times before its eventual commit incurs a timing overhead that might not be negligible and, therefore, must be taken into account to prevent deadline misses at runtime.

This work considers a set of potentially parallel real-time tasks sharing data and executed on a multi-core platform. Assuming this setting, first it proposes a complete framework where an STM service is associated to a set of fully partitioned scheduling algorithms in order to improve the predictability of the system as well as guaranteeing that the timing constraints are met for all the tasks. Then, it proposes the corresponding schedulability analysis for each pair of STM and scheduling algorithms. Finally, it proposes a lightweight syntax to enrich the original Ada programming language in order to support STM for concurrent real-time applications.

### Sumário

A tendência actual no desenvolvimento de sistemas de tempo-real embutidos é caracterizada por (i) ao nível do *hardware*, a transição de arquitecturas baseadas em um único processador para múltiplos processadores num circuito integrado; (ii) ao nível do *software* pela transição de paradigmas de programação sequenciais para paralelos; e, finalmente, (iii) pela sempre crescente necessidade de novas funcionalidades (por exemplo, tarefas adicionais com requisitos temporais). Estes factores tomados em conjunto aumentam a complexidade do sistema de um ponto de vista geral, tendo um impacto significativo nos mecanismos que são adoptados para garantir a correcção funcional e não-funcional do sistema. Isto é especialmente verdadeiro no caso em que tais mecanismos têm que manter a correcção dos dados partilhados entre diferentes tarefas concorrentes executadas em paralelo.

O acesso a recursos partilhados (por exemplo, a memória principal) em sistemas com um único processador tem sido tradicionalmente gerido por mecanismos de bloqueio (habitualmente denominados de *locks*), i.e. estruturas que permitem bloquear temporariamente o acesso a esses recursos a pedido das tarefas. Em qualquer instante, o acesso a um recurso partilhado é apenas permitido em exclusivo a uma única tarefa. No entanto, assumindo o novo cenário de arquitecturas baseadas em múltiplos processadores num circuito integrado a executar um conjunto de tarefas potencialmente em paralelo, acedendo a dados partilhados em memória modifica o panorama em que assenta o desenvolvimento de sistemas. A execução de tarefas em paralelo em diferentes processadores que acedem aos mesmos dados poderão ter que competir entre elas até finalmente terminarem a sua execução. Infelizmente, a sincronização de tarefas baseada em mecanismos de bloqueio que são eficazes em sistemas mono-processador não são eficientes em arquitecturas com múltiplos processadores e, além do mais, têm um impacto negativo na composição do sistema.

As abordagens baseadas no conceito da *Software Transactional Memory* (STM) foram propostas como possíveis candidatos para resolver os problemas previamente mencionados. A utilização destas técnicas alternativas implicam um serviço que resolve conflitos entre tarefas concorrentes de forma a manter a consistência dos dados, enquanto as secções críticas das tarefas são executadas especulativamente – i.e. o resultado da execução da secção crítica pode ser descartado se comprometer a consistência dos dados. Desta forma, os detalhes sobre *como* sincronizar dados partilhados tornam-se transparentes para o programador, representando uma vantagem significativa sobre os mecanismos de bloqueio, do ponto de vista da correcção funcional do sistema. Mas no que toca à correcção não-funcional, é necessário que a utilização de abordagens baseadas em STM garantam que as restrições temporais das tarefas sejam respeitadas. Isto deve-se ao facto de que abortar e repetir uma transação múltiplas vezes até finalmente concluir com sucesso implica custos adicionais em tempo de execução que poderão ser significativos, que poderão traduzir-se em tarefas a ultrapassar os seus prazos em tempo de execução.

Esta tese considera um conjunto de tarefas com características de tempo-real, potencialmente paralelas, que partilham dados em memória, executadas numa plataforma com múltiplos processadores num circuito integrado. Assumindo este cenário, em primeiro lugar propõe uma estrutura

completa em que um serviço de STM é associado a um conjunto de algoritmos de escalonamento particionado, de forma a incrementar a previsibilidade do sistema e garantir que as restrições temporais de todas as tarefas são respeitadas. Depois, propõe a respectiva análise de escalonabilidade para cada associação de STM vs. algoritmo de escalonamento. Por fim, propõe uma sintaxe para aumentar a linguagem de programação Ada, de forma a suportar STM no desenvolvimento de aplicações concorrentes de tempo-real.

# Acknowledgements

First, I would like to express my deepest gratitude to my supervisor, Prof. Luís Miguel Pinho, for giving me the opportunity to work with him and undertake this research work. His guidance, support, motivation and care were crucial to overcome the many obstacles that we faced along the way, and complete this personal endeavour. I always felt comfortable to discuss any topics and issues with Miguel, and I am aware and grateful for all I have learned due to this kind openness. I must stress that Miguel demands no less than high standards, which occasionally made me quite nervous, thinking on how to properly handle the task in hand. But I must stress even more how he always encouraged me and pushed me to carry on when work seemed overwhelming.

I am immensely grateful to Patrick Meumeu Yomsi, who is in fact acting as a co-supervisor. We started working together only in 2015 but yet, much of him is in this thesis, as he helped me in so many, many ways. Always with a smile, he seriously motivated me to do things *the right way* – "Keep pushing, man!" – and this is reflected in this manuscript. I learned a lot from Patrick, and I certainly improved myself a lot with him.

I am very lucky to have these two great men as friends.

Thanks to my colleagues and friends at CISTER. I would like to acknowledge Eduardo Tovar for creating such a dynamic and challenging and yet, friendly and cosy environment. I would like to thank my colleagues for all the great ideas we discussed, but also for all the coffee break chit-chats that so many times help us to resume work with a much better state of mind, especially Ricardo Severino, Gurulingesh Raravi, Dakshina Dasari, Hossein Fotouhi, Maryam Vahabi, Ricardo Garibay-Martínez, Muhammad Ali Awan, Hazem Ali and Cláudio Maia. A special thanks for Paulo Baltarejo Sousa for all the help dealing with the linux kernel: I can't pay you all those days we spent programming, debugging, recompiling the kernel.

I also want to express my deepest gratitude to ISEP for all the institutional support to this PhD work, and to the Department of Informatics Engineering for doing everything to alleviate me as much as it was possible from my teaching-related labour, so I could pursue this endeavour. I deeply acknowledge my colleagues for their support and comprehension.

Finally I want express my infinite gratitude to my family. To my parents for their unconditional love, and who have always encouraged me to put my best on all the things I do. To my parents and parents-in-law for loving my daughters Núria and Alícia so much, and helping me with al those "small" daily tasks that represent so much. And specially to my wife, Dulce, who always believed in me, even when I was not so sure I could complete this thesis. I am aware of all the sacrifices she endured these last years. There are no words to thank for all the encouragement and companionship I received from Dulce.

António Barros

# List of publications

### Journal papers included in this thesis

António Barros, Luis Miguel Pinho, Patrick Meumeu Yomsi. Non-preemptive and SRP-based fully-preemptive scheduling of real-time Software Transactional Memory. *Journal of Systems Architecture (JSA)*, 61(10):553–566, Nov 2015.

### Conference or Workshop papers included in this thesis

- António Barros, Patrick Meumeu Yomsi, Luis Miguel Pinho. Response time analysis of hard real-time tasks sharing software transactional memory data under fully partitioned scheduling. In Proceedings of the 11th IEEE International Symposium on Industrial Embedded Systems (SIES 2016), Krakow, Poland, May 2016.

- António Barros, Luis Miguel Pinho. Non-preemptive scheduling of Real-Time Software Transactional Memory. In Proceedings of the Conference on Architecture of Computing Systems (ARCS 2014), Lübeck, Germany, February 2014.

- António Barros, Luis Miguel Pinho. *Revisiting Transactions in Ada*. In *Proceedings of the 15th International Real-Time Ada Workshop (IRTAW-15)*, pages 84-92, Fuente Dé, Spain, September 2011.

- António Barros, Luis Miguel Pinho. Software transactional memory as a building block for parallel embedded real-time systems. In Proceedings of the 37th EUROMICRO Conference on Software Engineering and Advanced Applications (SEAA 2011), pages 251–255, Oulu, Finland, September 2011.

- António Barros, Luis Miguel Pinho. Managing contention of software transactional memory in real-time systems. In Proceedings of the 31st IEEE Real-Time Systems Symposium (RTSS 2010), Work-In-Progress Session, San Diego, U.S.A., December 2010.

To Núria and Alícia.

# **Contents**

| 1 | Intr | oduction                                                         | 1  |

|---|------|------------------------------------------------------------------|----|

|   | 1.1  | Problem definition                                               | 3  |

|   | 1.2  | Relevance of the subject                                         | 5  |

|   | 1.3  | Main thesis preposition                                          | 7  |

|   | 1.4  | Thesis contributions                                             | 7  |

|   | 1.5  | Outline                                                          | 8  |

| 2 | Bacl | kground on real-time embedded systems                            | 11 |

|   | 2.1  | Modelling real-time systems                                      | 12 |

|   | 2.2  | Modelling the computing platform                                 | 15 |

|   | 2.3  | Real-time scheduling paradigms                                   | 17 |

|   | 2.4  | Relevant works in the real-time scheduling theory                | 23 |

|   | 2.5  | Summary                                                          | 27 |

| 3 | Bacl | kground on synchronisation mechanisms                            | 29 |

|   | 3.1  | Lock-based synchronisation                                       | 30 |

|   | 3.2  | Non-blocking data structures                                     | 36 |

|   | 3.3  | Transactional memory                                             | 38 |

|   | 3.4  | Relevant works on software transactional memory                  | 41 |

|   | 3.5  | Summary                                                          | 44 |

| 4 | Syst | em model                                                         | 45 |

|   | 4.1  | Task specifications                                              | 45 |

|   | 4.2  | Platform and Scheduler specifications                            | 46 |

|   | 4.3  | STM specifications                                               | 46 |

| 5 | FIF  | O-CRT: a predictable STM contention management                   | 49 |

|   | 5.1  | Requirements                                                     | 49 |

|   | 5.2  | Classical contention management policies                         | 50 |

|   | 5.3  | Discussion of criteria                                           | 52 |

|   | 5.4  | FIFO-CRT: a predictable contention manager for real-time systems | 56 |

|   | 5.5  | Summary                                                          | 59 |

| 6 | Scho | eduling tasks and transactions under FIFO-CRT                    | 61 |

|   | 6.1  | Impact of the scheduling policy on the contention manager        | 61 |

|   | 6.2  | Non-preemptive approaches                                        | 62 |

|   |      | 6.2.1 Non preemptible until commit (NPUC)                        | 63 |

|   |      | 6.2.2 Non preemptible during attempt (NPDA)                      | 65 |

|   | 63   | Praemytive approach (SDDTM)                                      | 65 |

xii CONTENTS

|    |      | 6.3.1    | Assigning preemption levels to tasks and to transactions 67              |

|----|------|----------|--------------------------------------------------------------------------|

|    |      | 6.3.2    | Scheduling policy                                                        |

|    | 6.4  | Summa    | ry                                                                       |

| 7  | Caba | dulahili | ty analysis of tasks under NPDA, NPUC and SRPTM 73                       |

| ,  |      |          |                                                                          |

|    | 7.1  |          | analysis for NPDA                                                        |

|    | 7.2  |          | analysis for NPUC                                                        |

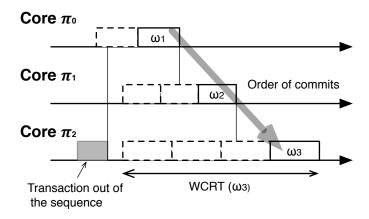

|    |      | 7.2.1    | WCRT of transaction $\omega_i$                                           |

|    |      | 7.2.2    | WCRT of task $\tau_i$                                                    |

|    | 7.3  |          | analysis for SRPTM                                                       |

|    |      | 7.3.1    | WCRT of transaction $\omega_i$                                           |

|    |      | 7.3.2    | WCRT of task $\tau_i$                                                    |

|    | 7.4  | Summa    | ury                                                                      |

| 8  | Eval | uation   | 87                                                                       |

| U  | 8.1  |          | rative evaluation                                                        |

|    | 0.1  | 8.1.1    | Simulation set up                                                        |

|    |      |          | 1                                                                        |

|    | 0.0  | 8.1.2    | Simulation results                                                       |

|    | 8.2  |          | tive evaluation                                                          |

|    |      | 8.2.1    | Deadlock                                                                 |

|    |      | 8.2.2    | Livelock                                                                 |

|    |      | 8.2.3    | Access to multiple objects per atomic section                            |

|    |      | 8.2.4    | Composability                                                            |

|    |      | 8.2.5    | Transparency                                                             |

|    |      | 8.2.6    | Priority inversion                                                       |

|    |      | 8.2.7    | Convoy effect                                                            |

|    |      | 8.2.8    | Impact of the synchronisation mechanism on a multi-core architecture 104 |

|    |      | 8.2.9    | Platform dependency                                                      |

|    | 8.3  | Summa    | ury                                                                      |

| 9  | Imnl | lementa  | tion 111                                                                 |

| 9  | -    |          |                                                                          |

|    | 9.1  | _        | mental setup                                                             |

|    |      |          | Platform specification                                                   |

|    |      | 9.1.2    | Task set generation                                                      |

|    |      | 9.1.3    | STM specification                                                        |

|    |      | 9.1.4    | Schedulers specification                                                 |

|    | 9.2  | Results  |                                                                          |

|    |      | 9.2.1    | STM performance                                                          |

|    |      | 9.2.2    | System performance                                                       |

|    |      | 9.2.3    | Response Time Analysis (RTA) accuracy                                    |

|    | 9.3  | Summa    | ury 154                                                                  |

| 10 | Cone | clusions | 159                                                                      |

| 10 |      |          | rry of results                                                           |

|    | 10.1 |          | Fair and predictable contention management algorithm                     |

|    |      |          |                                                                          |

|    |      |          | $\epsilon$                                                               |

|    | 10.2 |          | Response time analysis                                                   |

|    | 10.2 | ruture   | directions                                                               |

| References |     |                                                     | 165 |

|------------|-----|-----------------------------------------------------|-----|

| A          | Ada | language support for transactions                   | 175 |

|            | A.1 | State of the art                                    | 175 |

|            | A.2 | Ada language support for transactions               | 177 |

|            |     | A.2.1 Transactional object                          | 177 |

|            |     | A.2.2 Transaction identifier                        | 178 |

| В          | Bou | nded-memory multi-version STM for real-time systems | 181 |

xiv CONTENTS

# **List of Figures**

| 2.1 | Typical embedded system building blocks                                                          | 12  |

|-----|--------------------------------------------------------------------------------------------------|-----|

| 2.2 | Two multi-core processors for embedded applications                                              | 16  |

|     | a Tilera TILE-Gx8072                                                                             | 16  |

|     | b Kalray MPPA-256                                                                                | 16  |

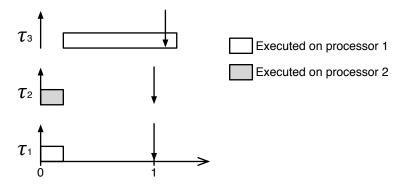

| 2.3 | Dhall's effect. Job $\tau_3$ misses the deadline because it cannot use the available ca-         |     |

|     | pacity of the two processors when they overlap in time                                           | 21  |

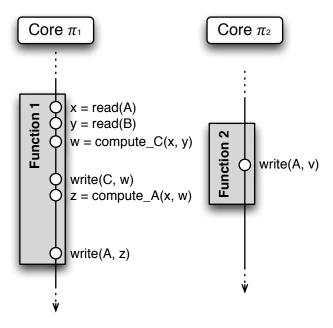

| 3.1 | Race condition                                                                                   | 31  |

| 3.1 | Priority inversion.                                                                              | 33  |

| 3.2 |                                                                                                  | 33  |

|     |                                                                                                  | 33  |

|     | b Bounded priority inversion                                                                     | 33  |

| 4.1 | Transaction dependencies by object concurrency                                                   | 47  |

| 4.2 | State diagram of a transaction                                                                   | 48  |

| 5.1 | Contention management based on number of aborts                                                  | 52  |

| 5.2 | Live-lock due to laxity criteria                                                                 | 54  |

| 5.3 | Contention management based on transaction release times                                         | 55  |

| 5.4 | Contention between transactions on the same core resulting in deadlock                           | 56  |

| 5.5 | Contention management based on job absolute deadlines                                            | 58  |

| 5.5 | Contention management based on job absorate deadlines                                            | 50  |

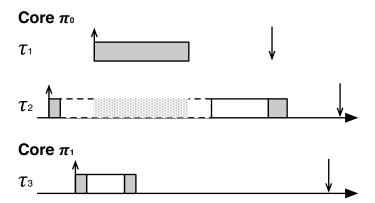

| 6.1 | A preempted transaction with earlier release time being aborted                                  | 62  |

| 6.2 | Long transaction is excessively aborted because of preemptions                                   | 63  |

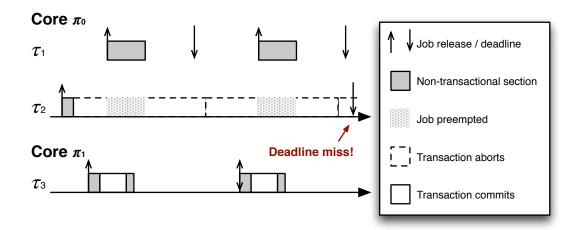

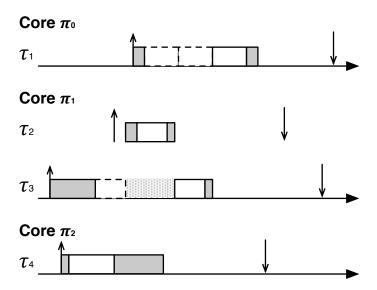

| 6.3 | Transactions scheduled under NPUC                                                                | 64  |

| 6.4 | Contention cascades                                                                              | 65  |

| 6.5 | Transactions scheduled under NPDA                                                                | 66  |

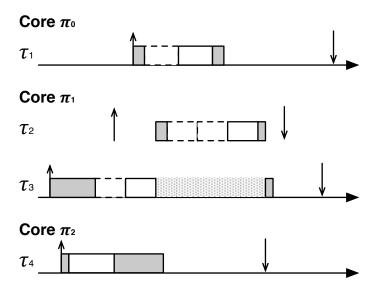

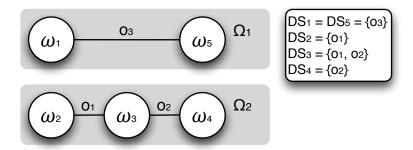

| 6.6 | Transaction dependencies by object concurrency                                                   | 68  |

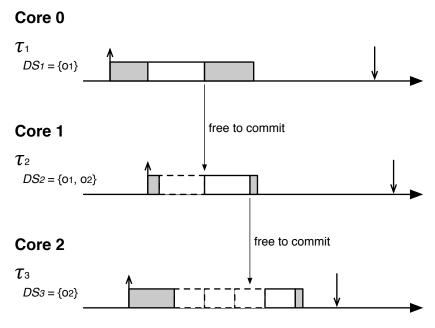

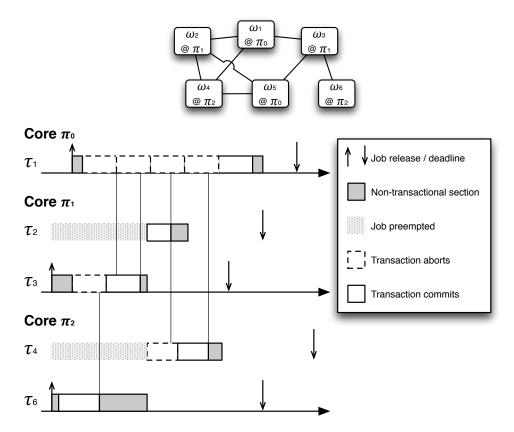

| 7.1 | Preempted jobs executing $\omega_2$ and $\omega_4$ are rescheduled in times to abort transaction |     |

| ,   | $\omega_1$                                                                                       | 74  |

| 7.2 | Sequence of transactions until $\omega_1$ commits                                                | 76  |

| 7.3 | $\omega_1$ , the first transaction in the sequence aborts once before commits                    | 77  |

| 0.1 |                                                                                                  | 0.1 |

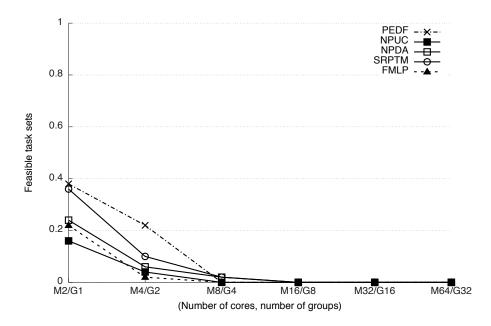

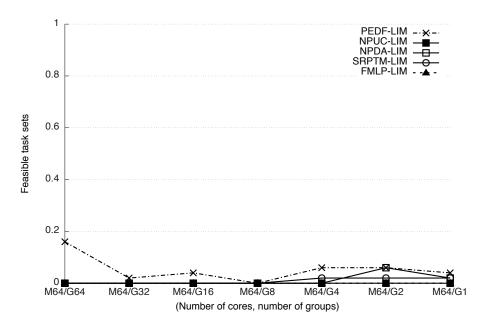

| 8.1 | Feasibility rates: varying number of cores                                                       | 91  |

| 8.2 | Feasibility rates: varying number of cores with smaller atomic sections                          | 92  |

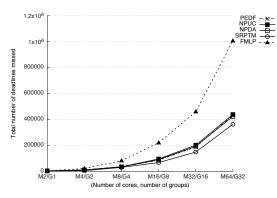

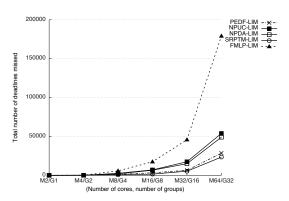

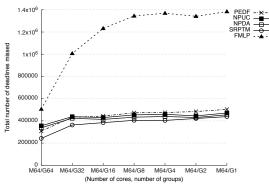

| 8.3 | Total number of deadline misses (50 simulations)                                                 | 93  |

|     | a Atomic sections with unrestricted size                                                         | 93  |

|     | b Smaller atomic sections                                                                        | 93  |

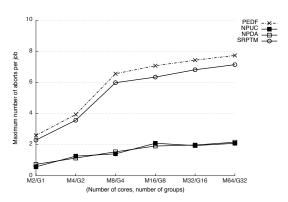

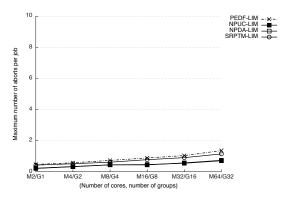

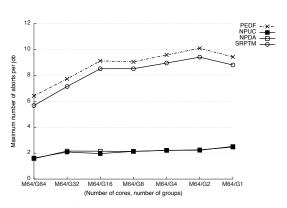

| 8.4 | Maximum number of aborts per job (average)                                                       | 93  |

xvi LIST OF FIGURES

|      | a Atomic sections with unrestricted size                                | 93  |

|------|-------------------------------------------------------------------------|-----|

|      | b Smaller atomic sections                                               | 93  |

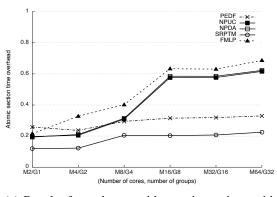

| 8.5  | Time overhead per atomic section (average)                              | 93  |

|      | a Atomic sections with unrestricted size                                | 93  |

|      | b Smaller atomic sections                                               | 93  |

| 8.6  | Feasibility rates: varying number of cores with smaller atomic sections | 94  |

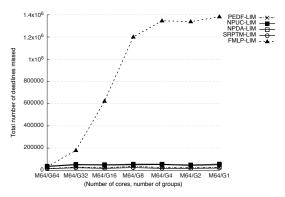

| 8.7  | Total deadlines missed (50 simulations)                                 | 95  |

|      | a Atomic sections with unrestricted size                                | 95  |

|      | b Smaller atomic sections                                               | 95  |

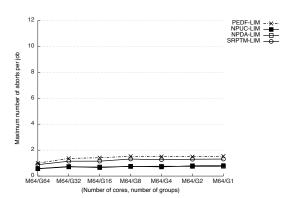

| 8.8  | Maximum number of aborts per job (average)                              | 95  |

|      | a Atomic sections with unrestricted size                                | 95  |

|      | b Smaller atomic sections                                               | 95  |

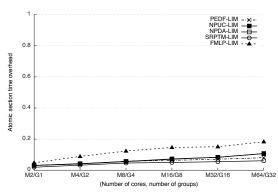

| 8.9  | Execution time overhead per atomic section (average)                    | 96  |

|      | a STM and lock-based results                                            | 96  |

|      | b Detailed view, excluding FMLP                                         | 96  |

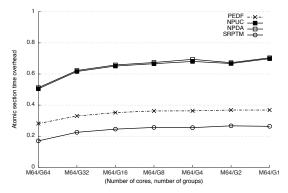

| 9.1  | STM transactional object descriptors.                                   | 114 |

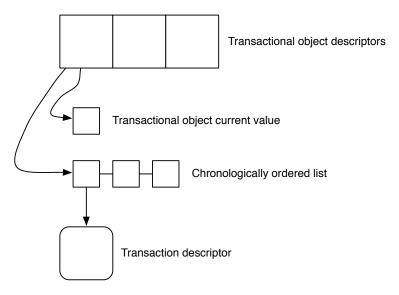

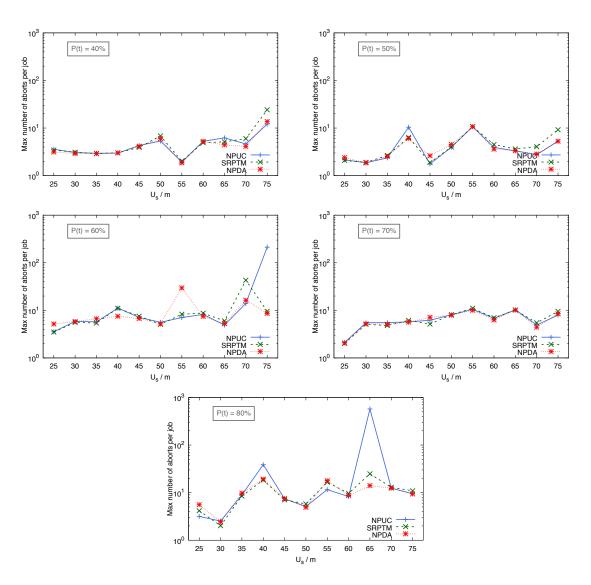

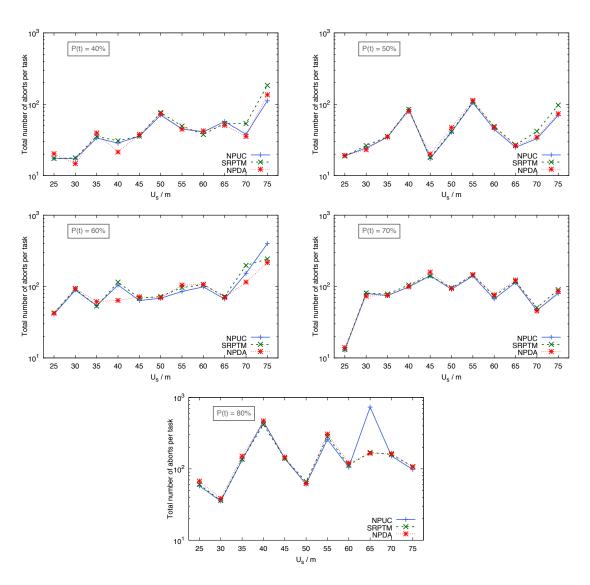

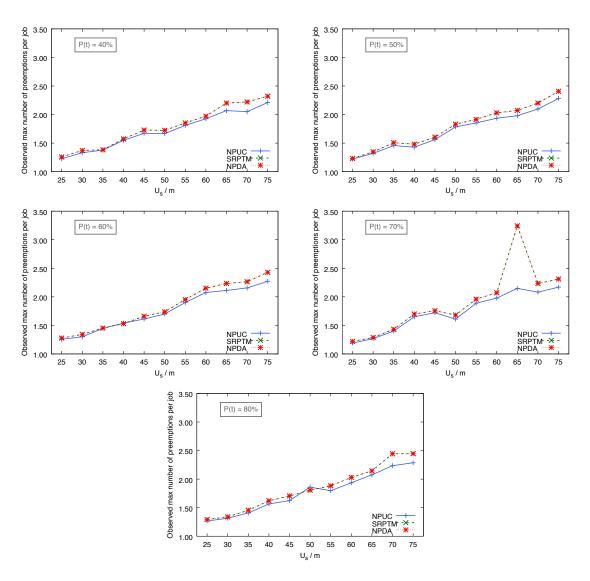

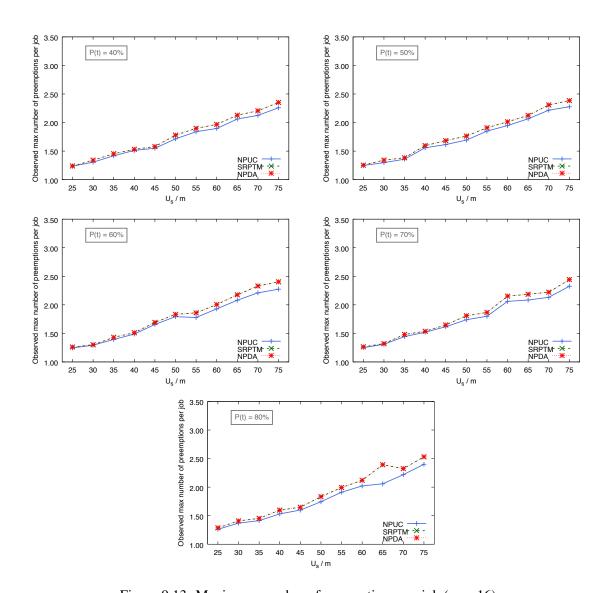

| 9.2  | Maximum number of aborts of a transaction per job $(m = 2)$             | 117 |

| 9.3  | Maximum number of aborts of a transaction per job $(m = 4)$             | 118 |

| 9.4  | Maximum number of aborts of a transaction per job $(m = 8)$             | 119 |

| 9.5  | Maximum number of aborts of a transaction per job ( $m = 16$ )          | 120 |

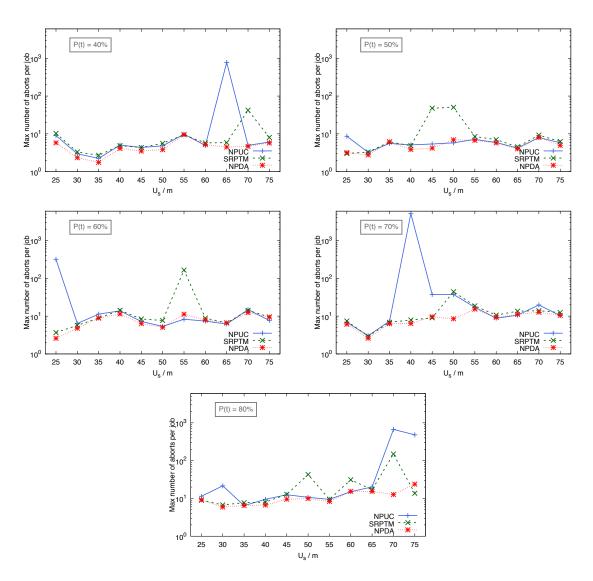

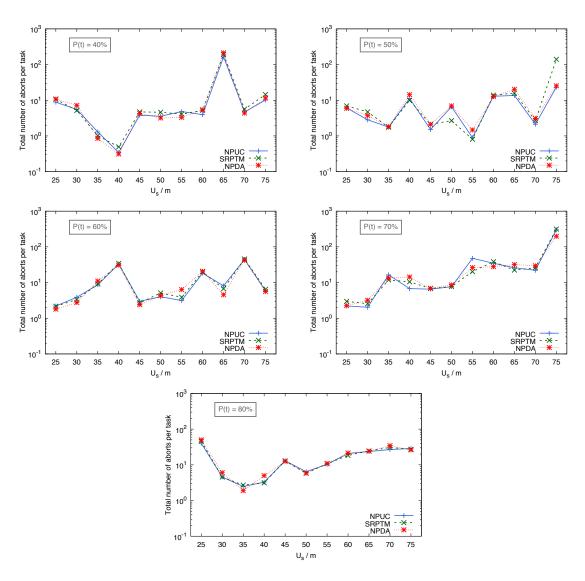

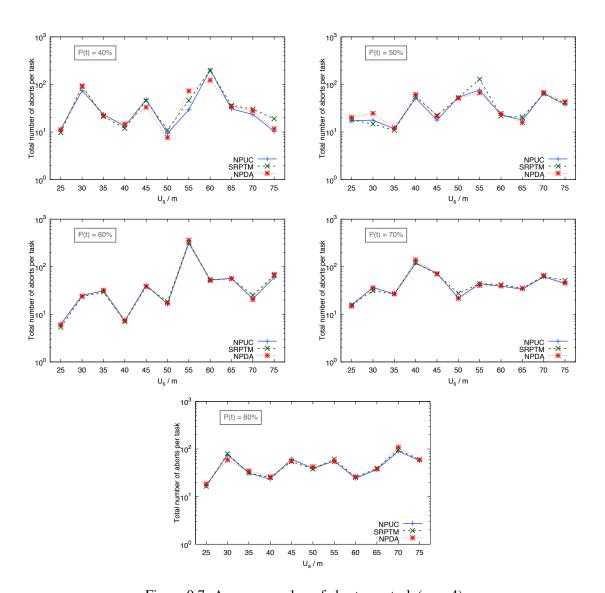

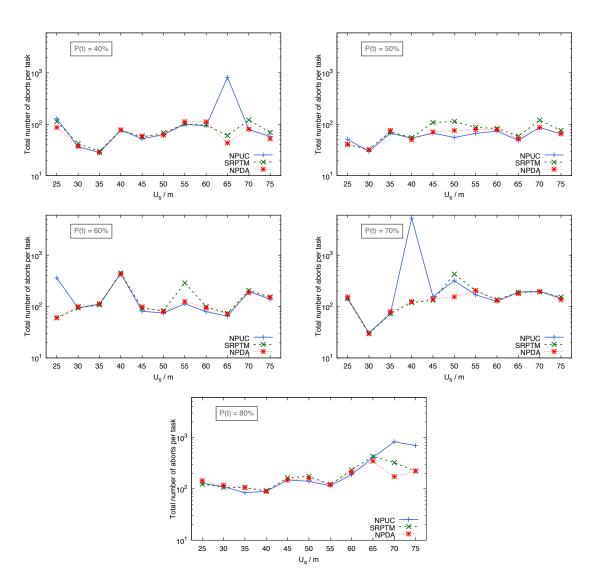

| 9.6  | Average number of aborts per task $(m = 2)$                             | 122 |

| 9.7  | Average number of aborts per task $(m = 4)$                             | 123 |

| 9.8  | Average number of aborts per task $(m = 8)$                             | 124 |

| 9.9  | Average number of aborts per task $(m = 16)$                            | 125 |

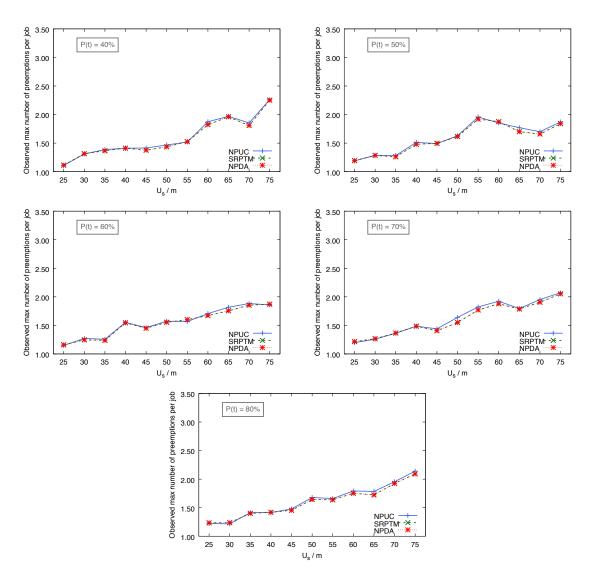

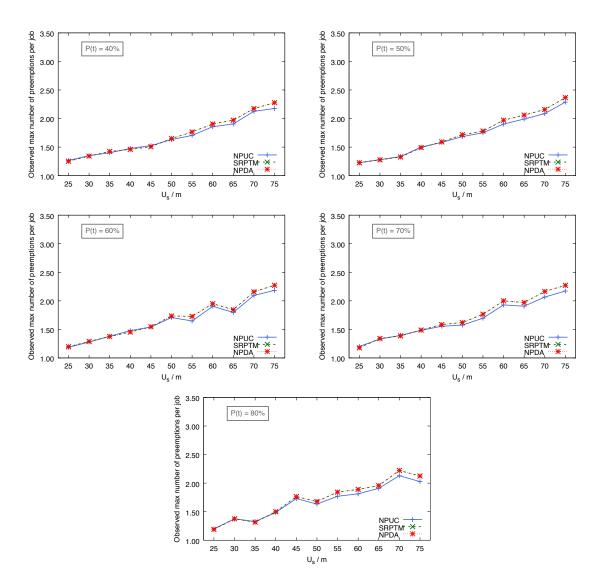

| 9.10 | Maximum number of preemptions per job $(m = 2)$                         | 126 |

| 9.11 | Maximum number of preemptions per job $(m = 4)$                         | 127 |

|      | Maximum number of preemptions per job $(m = 8)$                         | 128 |

|      | Maximum number of preemptions per job $(m = 16)$                        | 129 |

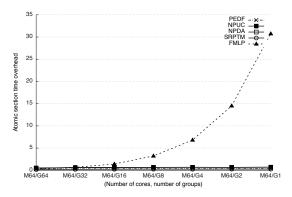

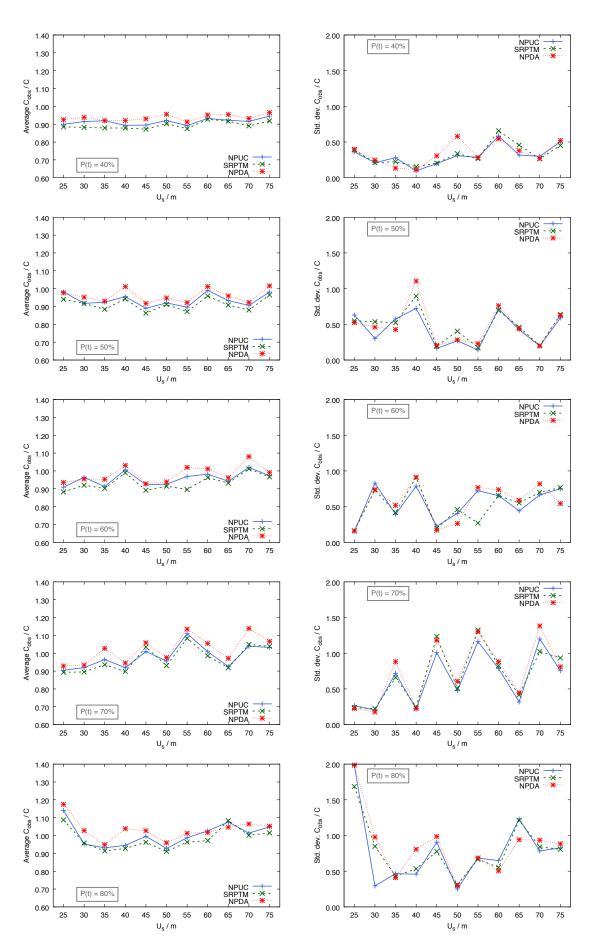

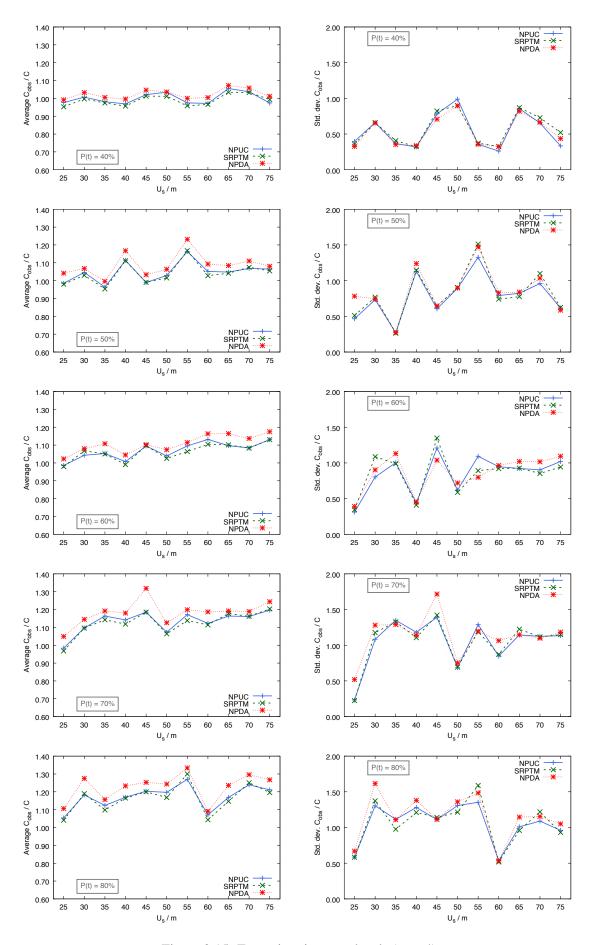

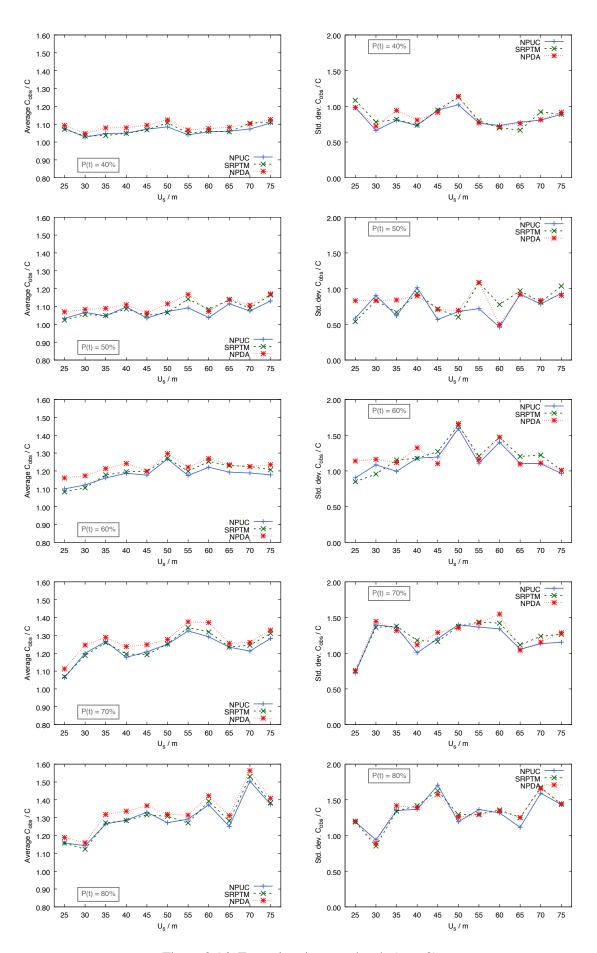

|      | Execution time overheads $(m = 2)$                                      | 131 |

| 9.15 | Execution time overheads $(m = 4)$                                      | 132 |

|      | Execution time overheads $(m = 8)$                                      | 133 |

|      | Execution time overheads ( $m = 16$ )                                   | 134 |

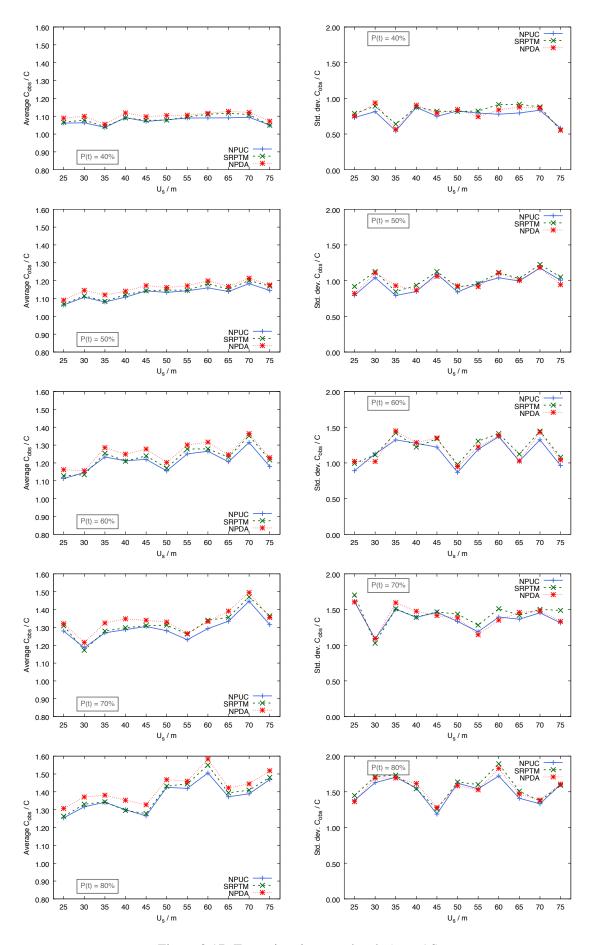

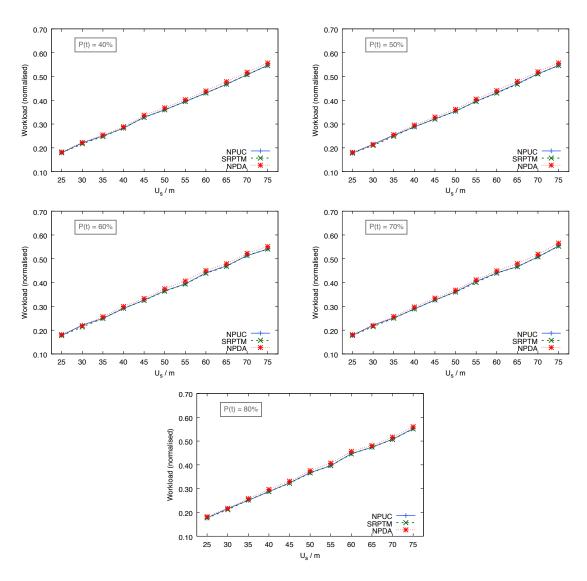

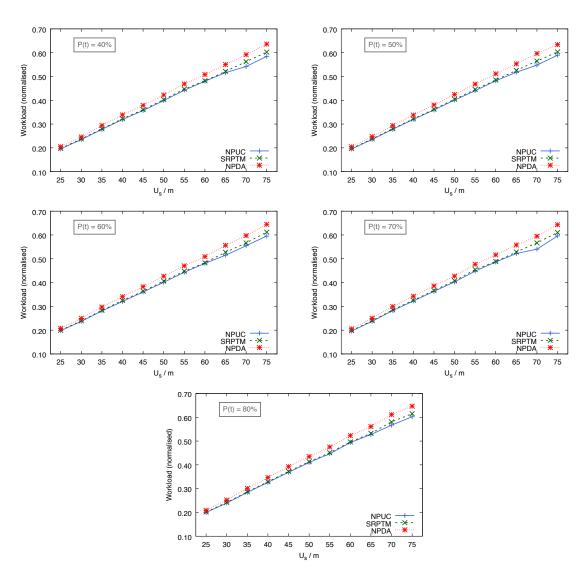

|      | Workload (normalised by the number of tasks) $(m = 2)$                  | 136 |

| 9.19 | Workload (normalised by the number of tasks) $(m = 4)$                  | 137 |

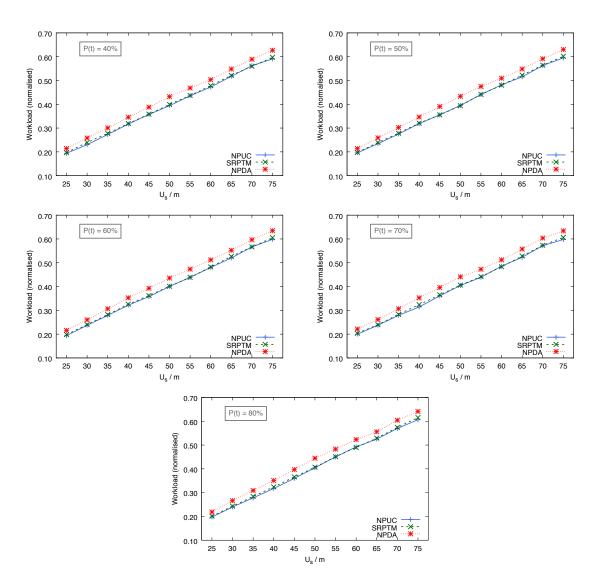

| 9.20 | Workload (normalised by the number of tasks) $(m = 8)$                  | 138 |

| 9.21 | Workload (normalised by the number of tasks) ( $m = 16$ )               | 139 |

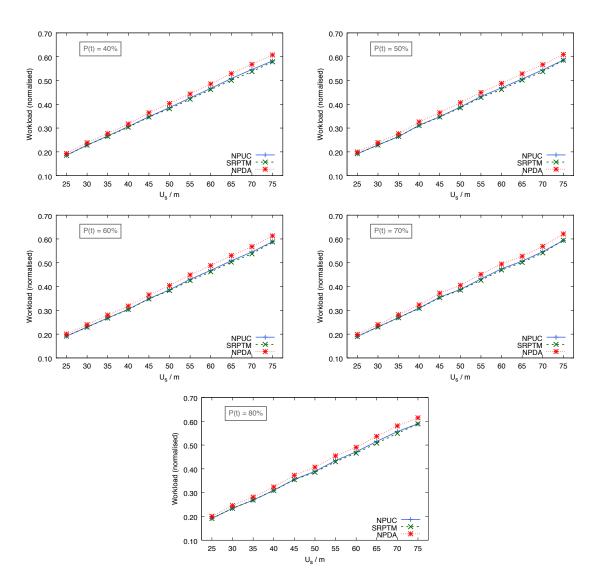

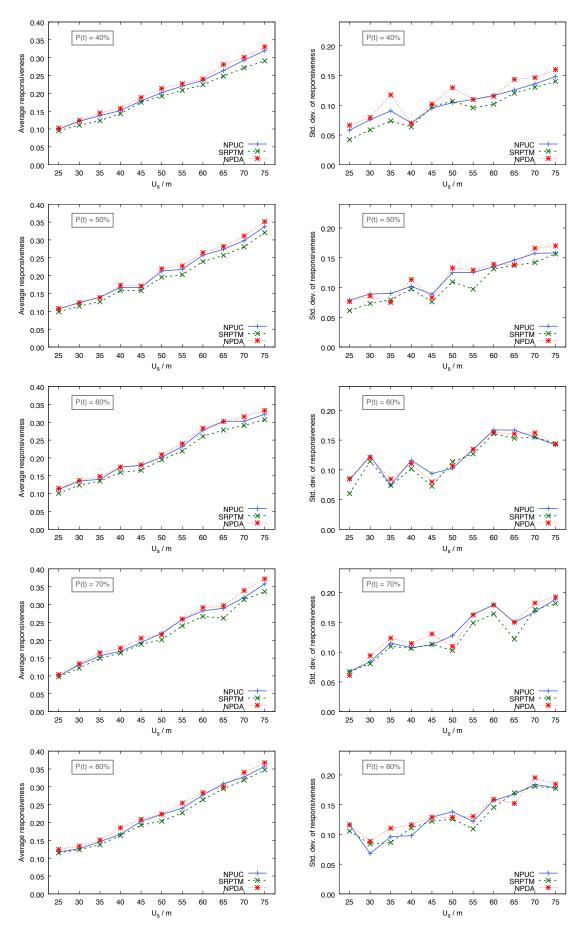

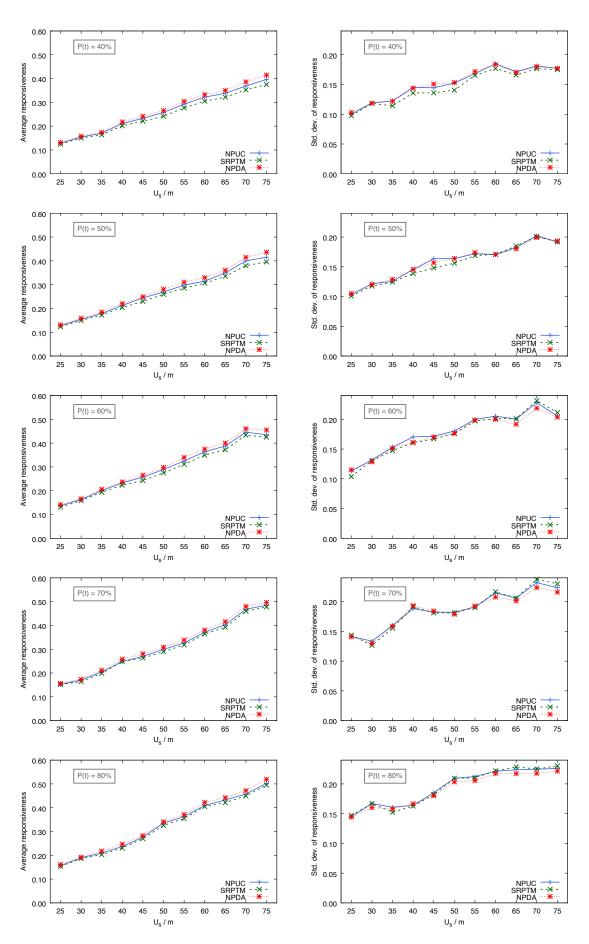

| 9.22 | Responsiveness $\frac{RT}{T}$ $(m=2)$                                   | 140 |

| 9.23 | Responsiveness $\frac{RT}{T}$ $(m=2)$                                   | 141 |

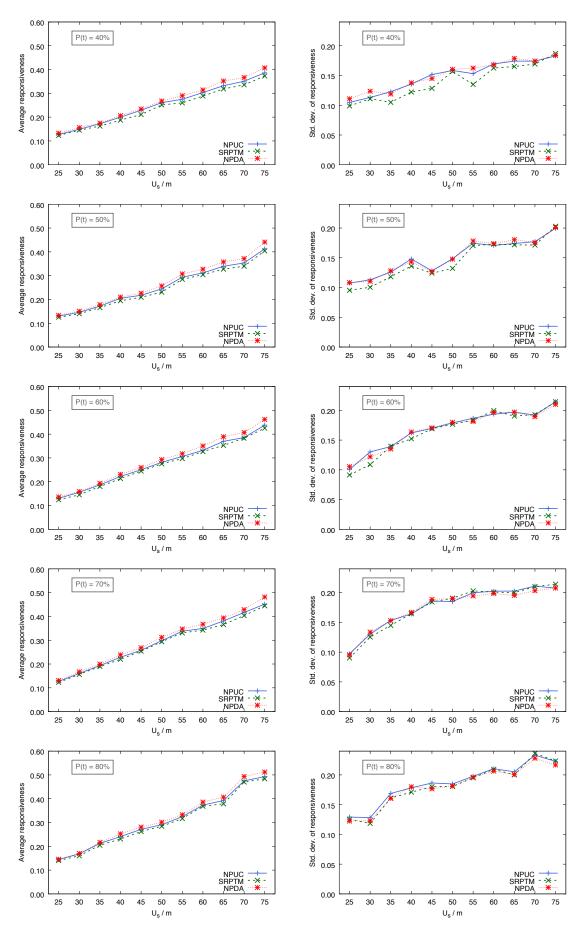

| 9.24 | Responsiveness $\frac{RT}{T}$ $(m=8)$                                   | 142 |

| 9.25 | Responsiveness $\frac{RT}{T}$ $(m = 16)$                                | 143 |

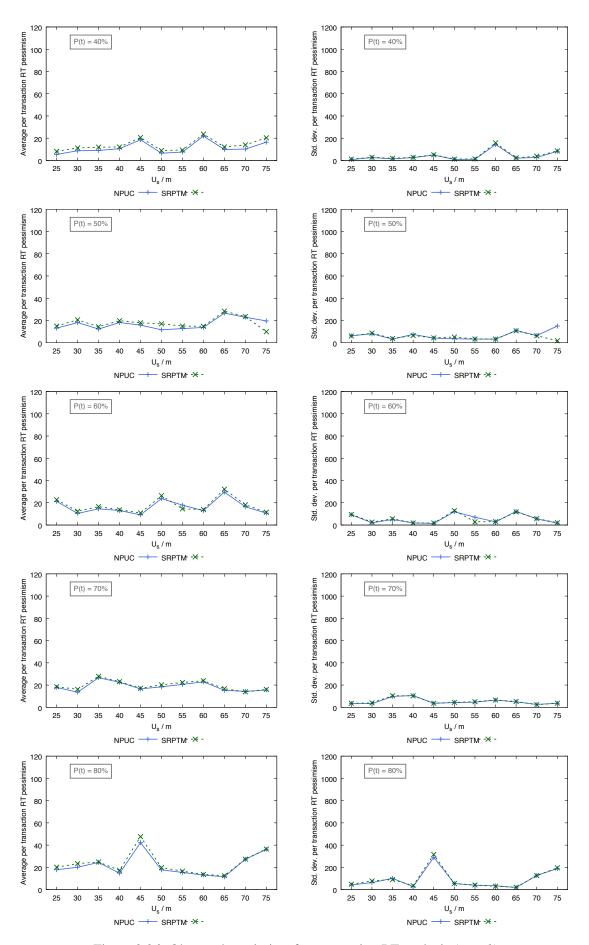

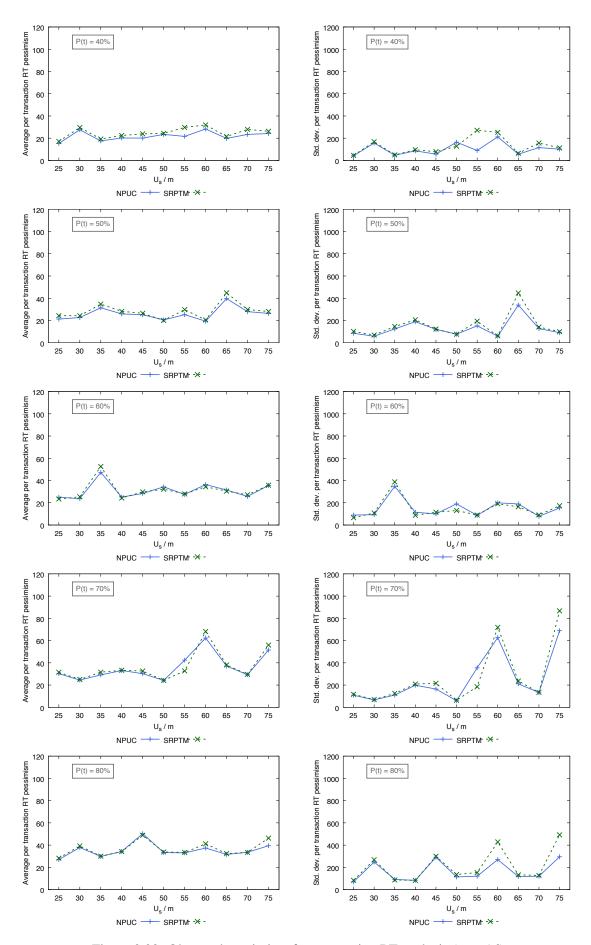

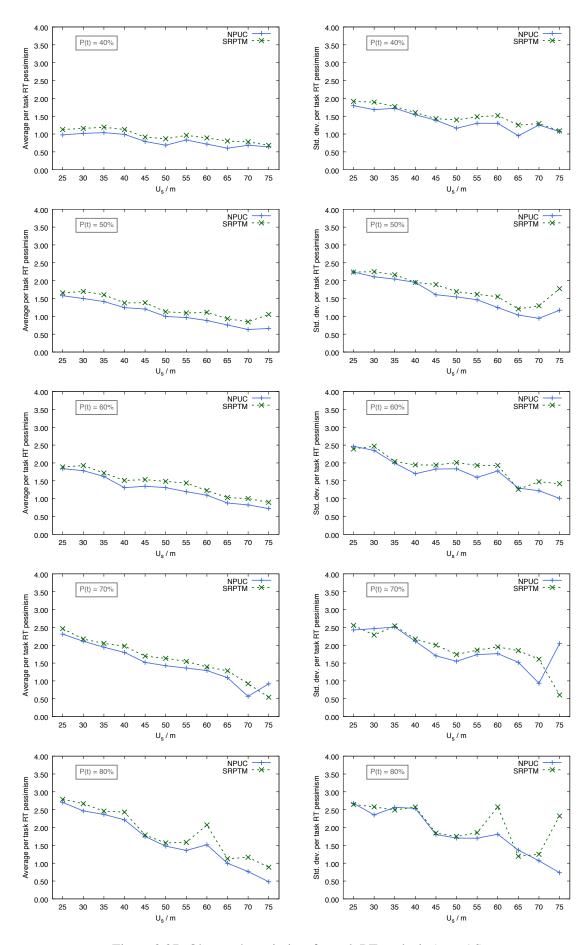

| 9.26 | Observed pessimism for transaction RT analysis ( $m = 2$ )              | 145 |

| 9.27 | Observed pessimism for transaction RT analysis ( $m = 4$ )              | 146 |

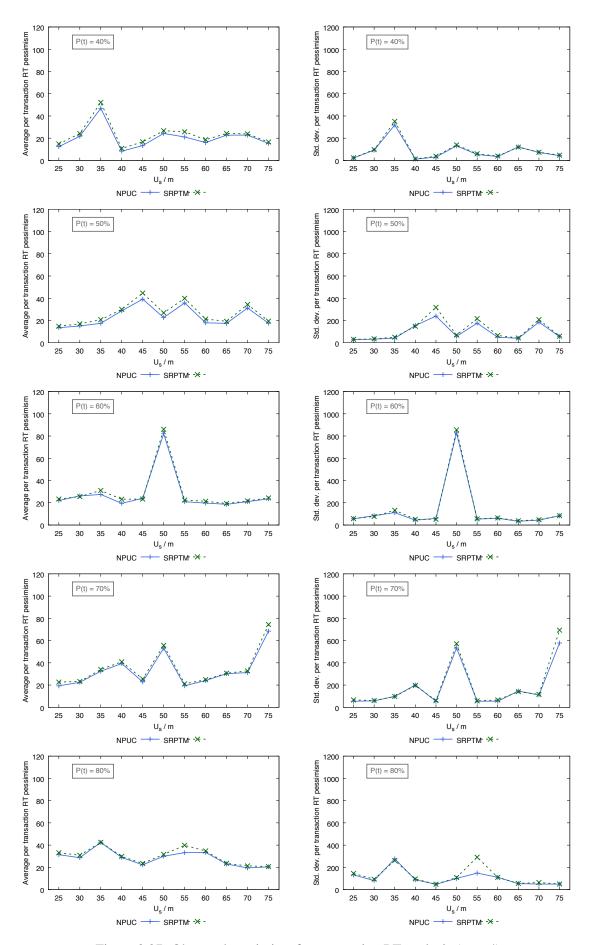

| 9.28 | Observed pessimism for transaction RT analysis ( $m = 8$ )              | 147 |

| 9.29 | Observed pessimism for transaction RT analysis ( $m = 16$ )             | 148 |

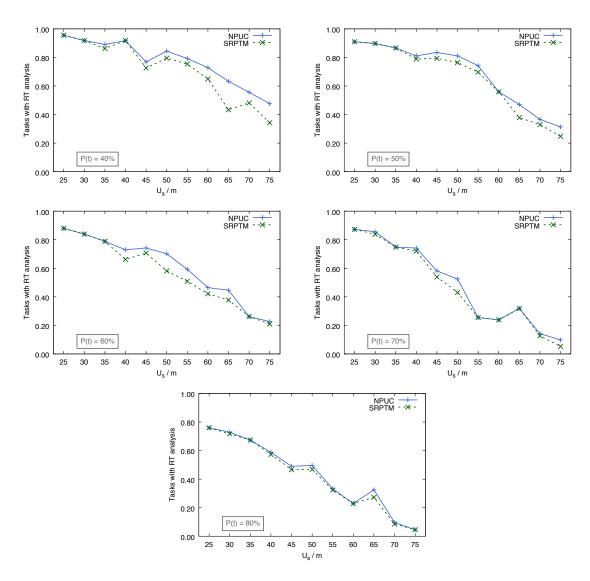

| 9.30 | Ratio of tasks that were RT analysed ( $m = 2$ )                        | 150 |

|      | Ratio of tasks that were RT analysed ( $m = 4$ )                        | 151 |

| 9.32 | Ratio of tasks that were RT analysed ( $m = 8$ )                        | 152 |

| 9 33 | Ratio of tasks that were RT analysed $(m = 16)$                         | 153 |

| LIST OF FIGURES | xvii |

|-----------------|------|

|                 |      |

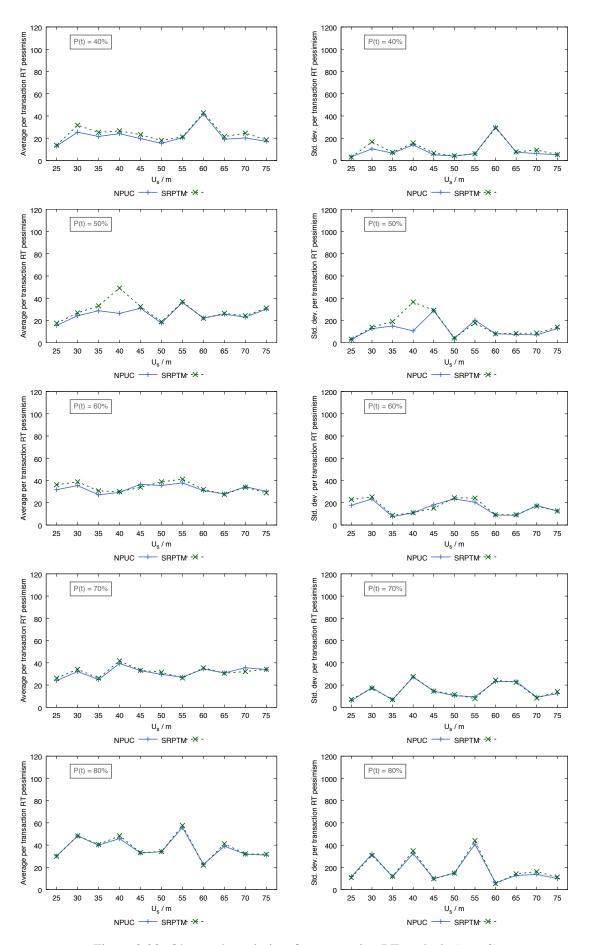

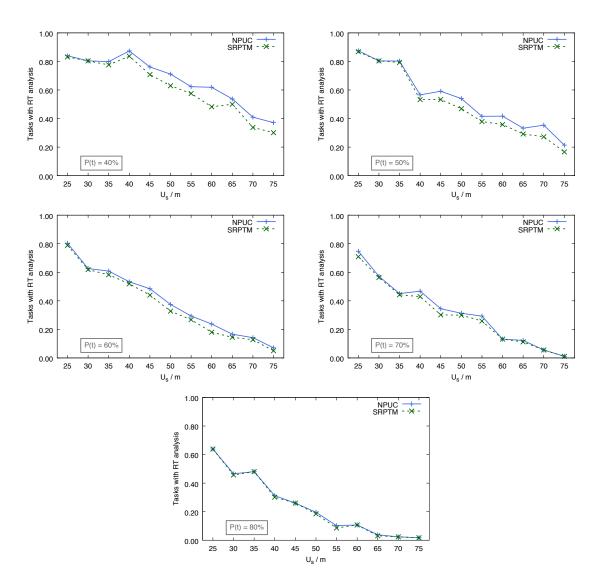

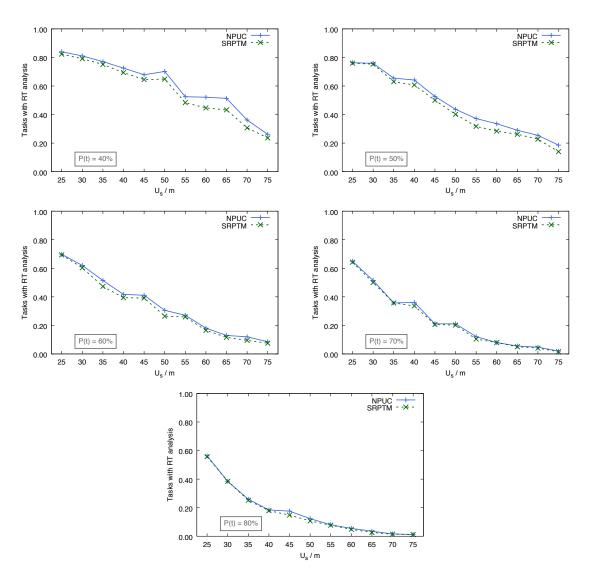

| 9.34 | Observed pessimism for task RT analysis ( $m = 2$ )                               | 155 |

|------|-----------------------------------------------------------------------------------|-----|

| 9.35 | Observed pessimism for task RT analysis $(m = 4)$                                 | 156 |

| 9.36 | Observed pessimism for task RT analysis $(m = 8)$                                 | 157 |

| 9.37 | Observed pessimism for task RT analysis ( $m = 16$ )                              | 158 |

|      |                                                                                   |     |

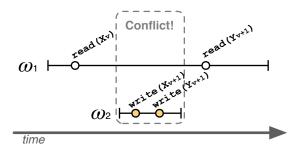

| B.1  | Conflict between a read-only $(\omega_1)$ and an update $(\omega_2)$ transactions | 182 |

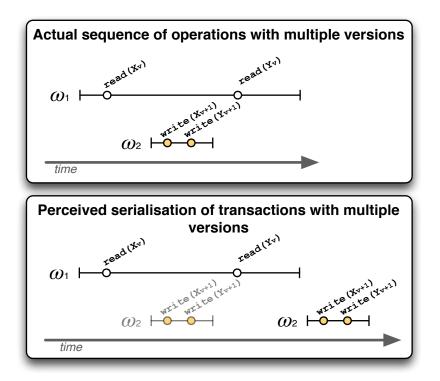

| B.2  | Conflict between a read-only $(\omega_1)$ and an update $(\omega_2)$ transactions | 182 |

xviii LIST OF FIGURES

# **List of Tables**

| 6.1 | Task parameters and transaction dependencies                                    | 69  |

|-----|---------------------------------------------------------------------------------|-----|

| 6.2 | Example of calculation of preemption levels                                     | 69  |

| 8.1 | Quantitative simulation results for 64 cores, 32 contention groups              | 109 |

| 8.2 | Summary of the qualitative evaluation of STM (opposed to locking) for real-time |     |

|     | embedded systems                                                                | 109 |

xx LIST OF TABLES

# **Acronyms and Symbols**

### List of acronyms

ASTM Adaptive STM

BF Best Fit

BFD Best Fit Decreasing

BHP Bounded direct blocking with High Parallelism

CAS Compare-And-Swap

CM Contention Manager

DDR Double Data Rate synchronous dynamic random-access memory

DP Dynamic Priority scheduler

DS Data set

DSTM Dynamic STM

ECM EDF Contention Manager EDF Earliest Deadline First

FBLT First Bounded, Last Timestamp contention manager

FIFO First In, First Out

FIFO-CRT First In First Out Contention manager for Real-Time systems

FF First Fit

FFD First Fit Decreasing FP Fixed Priorities

FJP Fixed-Job Priority scheduler

FMLP Flexible Multiprocessor Locking Protocol

FTP Fixed-Task Priority scheduler G-EDF Global Earliest Deadline First

L1 Level-1 cache

L2 Level-2 cache

L3 Level-3 cache

LCM Length-based Contention Manager

LLF Least Laxity First

McRT-STM Multi-core RunTime STM

MIC Many Integrated Core architecture

MPB Message Passing Buffer

M-PCP Multiprocessor Priority Ceiling Protocol M-SRP Multiprocessor Stack Resource Protocol

MWCAS Multi-Word Compare-And-Swap

NoC Network on a Chip

NPDA Non-Preemptive During Attempt NPUC Non-Preemptive Until Commit NUMA Non-Uniform Memory Access

OMLP O(m) Locking Protocol

OSTM Object-based STM

PCP Priority Ceiling Protocol

PD Pseudo-Deadline Pfair algorithm

PD<sup>2</sup> PD algorithm with simplified tie-breaking mechanism

P-EDF Partitioned Earliest Deadline First

PF Proportionate Fair

Pfair Proportionate fair scheduling

P-FP Partitioned Fixed Priority

PIP Priority Inheritance Protocol

PNF Priority contention manager with Negative values and First access

P-PCP Parallel Priority Ceiling Protocol

QPA Quick convergence Processor-demand Analysis

RCM RMA Contention Manager

RM Rate Monotonic

RNLP Real-time Nested Locking Protocol

RR Round-Robin

RS Read set

R/W RNLP Multiple reads and mutually exclusive write Real-time Nested Locking Proto-

col

SCC Single-chip Cloud Computer

SRP Stack Resource Protocol

SRPTM SRP for Transactional Memory

STM Software Transactional Memory

TL2 Transactional Locking 2

U-EDF Unfair but Optimal Multiprocessor Scheduling Algorithm for Sporadic Tasks

UMA Uniform Memory Access

WCET Worst Case Execution Time

WCRT Worst Case Response Time

WF Worst Fit

WFD Worst Fit Decreasing WFI Worst Fit Increasing

WS Write set

### List of symbols

### Task set parameters.

$\tau$  A task set.

*n* The number of tasks of  $\tau$ .

$\tau_i$  The  $i^{th}$  task of  $\tau$ .

$C_i$  The worst-case execution time of  $\tau_i$ .  $T_i$  The minimum inter-arrival time of  $\tau_i$ .

$D_i$  The relative deadline of  $\tau_i$ .

$R_i$  The worst-case response time of  $\tau_i$ .

$U_i$  Task utilisation of  $\tau_i$ .  $U_{\tau}$  Task set utilisation of  $\tau$ . P Hyper-period of the task set.

#### Job parameters.

$\tau_{i,j}$  The  $j^{th}$  job of  $\tau_i$ .

$r_{i,j}$  The release time of  $\tau_{i,j}$ .

$d_{i,j}$  The absolute deadline of  $\tau_{i,j}$ .

$f_{i,j}$  The time instant at which  $\tau_{i,j}$  finishes executing.

$rt_{i,j}$  The response time of  $\tau_{i,j}$ .

$W_{i,j}$  Transaction overhead of job  $\tau_{i,j}$ .

$A_{i,j}$  Number of aborts of transaction  $\omega_i$  executed by job  $\tau_{i,j}$ .

#### Hardware platform parameters.

$\pi$  The set of cores.

m The number of cores of  $\pi$ .

$\pi_k$  The  $k^{th}$  core of  $\pi$ .

$\sigma(\tau_i)$  Function that returns the core to which  $\tau_i$  is assigned.

### Transaction parameters.

$\omega_i$  Transaction executed by task  $\tau_i$ .

$C_{\omega_i}$  The maximum execution time required to execute the sequential code of transaction  $\omega_i$

$C_{a-\omega_i}$  Execution time required by the non-transactional section of  $\tau_i$  executed before transaction  $\omega_i$ .

$C_{p-\omega_i}$  Execution time required by the non-transactional section of  $\tau_i$  executed after transaction  $\omega_i$ .

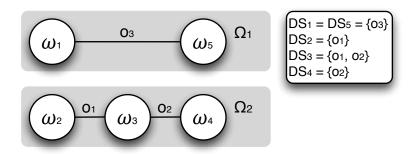

DS<sub>i</sub> Data set of  $\omega_i$ , i.e. the collection of transactional objects accessed by  $\omega_i$ .

RS<sub>i</sub> Read set of  $\omega_i$ , i.e. the collection of transactional objects accessed exclusively for reading by  $\omega_i$ .

WS<sub>i</sub> Write set of  $\omega_i$ , i.e. the collection of transactional objects accessed modified by  $\omega_i$ .

$|DS_i|$  Size of the data set of  $\omega_i$ .

$|RS_i|$  Size of the read set of  $\omega_i$ .

$|WS_i|$  Size of the write set of  $\omega_i$ .

### STM parameters.

O Set of STM objects.  $o_j$  The  $j_{th}$  object of O.

p The number of objects of O.

$|o_i|$  The number of transactions that access  $o_i$ .

### Contention group parameters.

G A contention graph, in which transactions are represented as vertices. Any two transactions that have intersecting data sets are connected by an edge.

$\Omega_a$  A contention group, i.e. a group of transactions that share intersecting data sets

$\Pi_a$  Subset of cores allocated to contention group  $\Omega_a$

$m_a$  The number of cores in  $\Pi_a$ .

### SRPTM.

$\lambda_i$  Preemption level of task  $\tau_i$ .

$\lambda_{\omega_i}$  Preemption level of transaction  $\omega_i$ .

$\Lambda_k$  Ceiling of core  $\pi_k$ .

$ceil(o_k)$  Ceiling of transactional object  $o_k$ .  $ceil(\Omega_g)$  Ceiling of contention group  $\Omega_g$ .

### NPUC analysis.

v(k) Transaction  $\omega_i$  on the  $k^{th}$  position in a given sequence of transactions ordered by their release times.

$R^{(k)}$  WCRT of a transaction  $\omega_i$  on the  $k^{th}$  position in a given sequence of transactions ordered by their release times.

$\mathcal{S}_i$  Set of all possible simple paths that converge to transaction  $\omega_i$ .

$\mathcal{S}_{i,k}$  Subset of all simple paths on length k that converge to transaction  $\omega_i$ .

$R_{\omega_i}$  Worst-case response time of transaction  $\omega_i$ .

$C_{\Omega_g,\pi_\ell}$  Longest execution time of all the transactions in contention group  $\Omega_g$  that are assigned to core  $\pi_\ell$ .

$I_{\Omega_g,\pi_k}$  Maximum inter-core interference that any transaction in contention group  $\Omega_g$  assigned to core  $\pi_k$  can experience.

$L_{a-\omega_i}$  Longest busy-period that occurs until transaction  $\omega_i$  is released.

$B_i$  Blocking term associated to lower priority tasks.

### SRPTM analysis.

$R_{a-\omega_i}$  Worst-case response time of the non-transactional section of code executed before transaction  $\omega_i$ .

$R_{\omega_i}^*$  Worst-case response time of the last two attempts of transaction  $\omega_i$ .

DB<sub>i</sub> The longest direct blocking term that task  $\tau_i$  can experience.

IB<sub>i</sub> The longest indirect blocking term that task  $\tau_i$  can experience.

## **Chapter 1**

### Introduction

Real-time systems are defined as those for which the correctness depends not only on the logical result of the computation, but also the time at which it is produced (Stankovic, 1988). When embedded in some form to control its environment, such a system consists of a set of tasks that interact and must process inputs from the environment in order to provide the adequate outputs within a pre-defined time window. This pre-defined time window is dictated by the requirements of the controlled system – i.e. the system's timing constraints. Examples of real-time systems include industrial computer-controlled systems, avionics applications such as airplane control, train braking systems, or real-time video processing such as the detection of people in front of a moving vehicle.

The timing constraints of a real-time system can be classified based on the consequences of meeting or not the timing requirements of each task (Burns, 1991). For a given system, when a task deadline miss may lead to a total failure of the entire system, then this task is referred to as a *hard real-time task*. When the integrity of the system is not at stake, that is the system can occasionally accommodate a few task deadline misses, but the benefit of this flexibility is drawn to zero after the deadline, i.e., the result produced is not useful, then the task is referred to as a *firm real-time task*. In the case the consequence of a task deadline miss is limited to a potential degradation of the Quality of Service (QoS) of the system, then the task is referred to as a *soft real-time task*. Obviously, a system may consist of a combination of all these three types of tasks. However, as soon as a single task has hard real-time requirements, then the whole system is stamped as *hard real-time*.

Traditional design of embedded real-time systems relies on the following assumptions about the external closed environment: (1) only a limited set of input sources is admissible, (2) only a limited set of functionalities is allowed and (3) only a limited set of output actions can be taken. With these assumptions, the design techniques often adopted for the allocation and management of the system resources in order to supply the pre-defined service requirements tend to be based on static rather than dynamic approaches (Klein et al., 1993). Following the trend described by

2 Introduction

Hansen et al. (2001), contemporary embedded real-time systems increasingly combine the requirements of traditional closed systems and the challenges of an open, heterogeneous, and dynamic environment. These systems have to cope with the dynamic evolution of the environment while maintaining a predefined quality of service.

Embedded architectures are following a major evolution. We have witnessed a paradigm shift from single core to multi-core platforms, due to thermal and capacitive limitations in Moore's Law prediction. The use of multi-core architectures in the embedded domain offers the ability to execute various tasks in parallel. However, the number of available cores significantly impacts the way these systems are implemented. Supporting the concurrency and the parallel interaction between tasks and the inherent use of data sharing mechanisms are tremendous challenges to account for in this case. These challenges exacerbate even more when it is necessary to guarantee the non-functional requirements of the application (Anderson et al., 2006). Therefore, it is essential to provide innovative and efficient mechanisms that allow developing dynamic applications while guaranteeing their reliability.

Instead of developing sequential code functions that are then made concurrent through operating system calls, it is well accepted that there are several advantages in writing concurrent programs with the semantics of concurrency in the programming language (Burns and Wellings, 2009). Real-time embedded applications interact with the external world (people, cars, robots, conveyor belts, planes, etc.) in situations that are inherently parallel and distributed. Their programs have to deal with various components like interrupt handlers (which react to internal/external events), clock handlers (which react to clock ticks) and managers (which monitors system state, task states and modes of operation). They also have to execute tasks corresponding to specific functionalities while taking into account real-world properties. If the concurrent nature of the system is explicitly supported by the semantics of the programming language, then the program becomes more readable, maintainable and reliable (Sutter and Larus, 2005). However, this feature comes along with a number of new problems, the language models and mechanisms for concurrent programming must be assessed in the same manner as the application functional and non-functional requirements are scrutinized.

In summary, the actual context for real-time embedded applications is characterised by the growing demands on functional requirements that results in an increase in the number of software components; and the shift from single-core to multi-core platforms which increases the complexity of the interactions between those components. Current approaches try to ease the development process by providing means to build correct applications through the selection and integration of correct components (composability) while ensuring the timing requirements. This approach hides from the programmer the interactions between components by applying mechanisms that maintain the consistency of shared data in a deterministic way. This can be achieved through programming languages and operating systems that expose the appropriate mechanisms for concurrent interaction and data sharing.

1.1 Problem definition 3

### 1.1 Problem definition

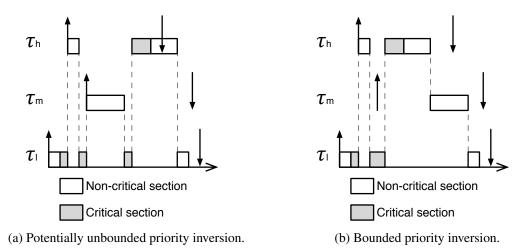

On single-core platforms, task interaction and access to shared resources traditionally rely on locking mechanisms (Anderson et al., 1997) such as semaphores (Dijkstra, 1965) and monitors (Hoare, 1974). These mechanisms became commonplace as means to provide sections of code, also referred to as a *critical section*, an exclusive access to shared resources. However, locking mechanisms come along with at least two challenges. The first challenge is the lack of composability (Sutter and Larus, 2005), i.e. correct components can be selected and when they are assembled together, they form a non-correct application; and the second challenge is the exposure to priority inversion in priority-based preemptive scheduling (Sha et al., 1990; Baker, 1991).

On multiprocessor systems, although additional computing resources are available on the platform, further issues arise. Locks can be classified according to their granularity. As such, we distinguish between: (1) the *coarse-grained locks* where a single lock controls the access to a large fraction of the available shared resources, and (2) the *fine-grained locks* where a single lock controls the access to a single or a small fraction of the available resources. Coarse-grained locks impede the progress of non-conflicting tasks that request access to the same lock, thus degrading the system throughput. On the other hand, fine-grained locks increase the complexity of system design because the same rule for acquiring locks must be applied across the whole system, thus hindering composability. Another issue is the *convoy effect* (Bershad, 1993). Here, a task that is holding a lock may have its execution paused or even halted (e.g. due to a preemption by a higher-priority task, an interruption by a event handler, or a core shut-down), thus delaying the completion time of all blocked tasks.

Currently, two directions are considered in order to tackle these issues. The first direction consists in adapting previous and/or devise new locking mechanisms for parallel systems, as proposed by Gai et al. (2001), Block et al. (2007), Easwaran and Andersson (2009a,b). The second direction consists in devising non-blocking mechanisms, as proposed by Tsigas and Zhang (1999), Anderson and Holman (2000), Brandenburg et al. (2008), Sarni et al. (2009), Cotard (2013) and El-Shambakey and Ravindran (2013b).

Adapting and/or devising new locking mechanisms is not a safe path to follow as they do not allow us to fully circumvent the hurdles previously discussed. In contrast, non-blocking mechanisms appear to be a suitable alternative as long as it is possible to include them in real-time systems. They are already used in distributed and highly-parallel systems with satisfactory results. They rely on the concept of *non-blocking data object*. Here, conflicting accesses are managed by an underlying mechanism that is responsible of maintaining the consistency of the shared data object. Every piece of code is written without critical sections, and as such a task will not block when it needs to access a resource.

On multiprocessor systems, non-blocking objects present strong conceptual advantages (Tsigas and Zhang, 1999). They have proven to perform better than lock-based solutions in several scenarios (Brandenburg et al., 2008). Priority inversion and deadlock are eliminated because accesses to the object proceed in parallel and concurrent accesses can always be resolved in favour of

4 Introduction

the higher-priority tasks. The convoy effect is also eliminated because no task will block, waiting for another task that is failing or prevented from executing. These advantages provided by non-blocking objects are somehow balanced by the complexity of the mechanisms that are required to maintain the consistency of each shared object. This complexity depends on the guarantee of progress provided by the non-blocking data object. This guarantee of progress can be classified in the following three categories: wait-free, lock-free or obstruction-free (Herlihy and Shavit, 2008), given with the following interpretation. A wait-free object ensures that every call will finish in a finite number of steps independently of the pace of execution of the other tasks. In this category, all tasks are ensured to progress. A lock-free object relaxes the progress condition, so that the system is broadly able to progress, although some tasks may suffer from starvation. In this category, any update of a data object will only take effect if no conflict occurs; otherwise, only one access is granted to complete, while the remaining contenders will fail and will be deemed to retry. An obstruction-free object ensures that one task will eventually progress if it executes in isolation relative to other contending tasks. Thus, this category provides the most relaxed guarantee of progress.

Despite the interesting features of non-blocking objects, critical sections usually provide atomicity to a composition of operations. A section of code that operates shared memory space in an atomic manner and with no explicit locks is referred to as a *transaction*. Herlihy and Moss (1993) described how to add extensions in the cache-coherence protocol of a multiprocessor architecture to implement the concept of *transactional memory*. In contrast to the approach proposed by Herlihy and Moss (1993) at the hardware level, Shavit and Touitou (1995) adapted the concept of transactional memory in order to implement all the synchronisation operations at the software level. They named it Software Transactional Memory (STM). The STM presents a huge advantage over the hardware-based approach: it is portable in the sense that it can be implemented seamlessly to multiple architectures; and it is hardware agnostic in the sense that there is no need to modify the circuitry of the chip. For this reason, to manage the access to shared memory regions we opted for STM-based techniques in this work.

The very first STM-based approach was proposed by Shavit and Touitou (1995) and only supported static transactions, i.e. transactions and memory locations are predefined before runtime. Later, other researchers proposed implementations of STM that support dynamical memory usage and dynamical transactions, i.e. each transaction can decide which addresses to access based on values read at runtime. However, the underlying synchronisation mechanisms are diverse. For example, Fraser's STM (Fraser, 2003) applies lock-free mechanisms. The Dynamic STM (DSTM) (Herlihy et al., 2003) uses obstruction-free mechanisms. Ennals' STM (Ennals, 2005) applies an optimistic concurrency control for reads, but uses locks to protect objects that will be written by a transaction. This STM approach is implemented along with a mechanism that avoids deadlock when deciding in favour of a determined transaction.

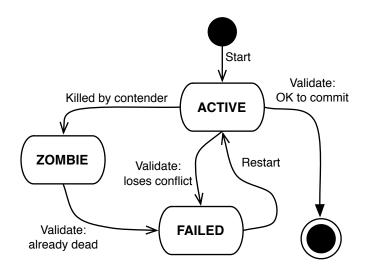

In general, a transaction is executed in isolation and must complete either by *committing* (i.e. when it succeeds) or by *aborting* (i.e. when it failed). This holds true irrespective of other transactions executing in parallel. In case of an abort, the transaction is deemed to retry. Data consistency

is maintained because transactions operate on private copies of shared data, so conflicting transactions will not race over the same data. Before completion, all accessed locations are checked for conflicting updates that may have occurred during the execution of the transaction. If no conflict is detected, then data is consistent and updates become effective. Otherwise, when a conflict has been detected, a contention policy is applied in order to allow, at least, one transaction to commit.

In order to achieve the intended guarantee of progress, every contention policy dictates how to solve conflicts among transactions. Typically, the contention policy must select the transaction to commit based on a criteria that meets the expected behaviour of the STM (Herlihy et al., 2003). It is also important that the contention policy avoids livelock, i.e. when two transactions are in conflict, they should not be able to abort each other indefinitely.

From the previous discussion, Software Transactional Memory is an interesting approach to solve the scalability and composability problems of lock-based approaches. Nevertheless, its use in real-time systems entails the support of appropriate mechanisms that would guarantee that all the timing requirements are met. The adopted contention policy must not only be functionally correct, but also its timing behaviour must be analysable. Furthermore, it should be possible to couple the programming model with the underlying implementation of these algorithms.

This thesis focuses on the problem of sharing data and synchronisation in concurrent real-time software executing on multi-core platforms.

### 1.2 Relevance of the subject

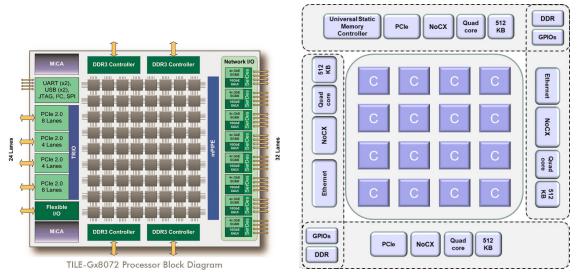

Because the traditional solution to increase the computing power of processors (i.e. reducing the size of components and increasing the clock frequency) reached physical limits (thermal and capacitive), chip manufacturers opted for packing multiple cores on a single chip. The current trend to push further in this direction is leading to massive multi-core or many-core processors. That is chips including tens to hundreds of cores, interconnected with switched networks. A few examples include the Tilera Tile64Pro which features 64 cores and the Tilera TiLE-Gx8072 which features 72 cores (Tilera, 2012, 2015); the Intel SCC which features 48 cores (Intel, 2010); the Intel Xeon Phi which features 60 cores (Intel, 2012); the Kalray MPPA featuring 256 cores (Kalray, 2015); and the Adapteva Epiphany featuring 1024 cores (Adapteva, 2012). These many-core architectures allow multiple applications to be deployed on the same chip, thus maximizing the hardware utilisation, and reducing the cost, size, weight, and power requirements. They also allow the designers to improve the performance of the applications through parallelism. Nevertheless, all this computing power raises a number of challenges, including the core-to-core and the coreto-memory communications. In addition, cache coherency becomes a cornerstone especially for platforms encompassing a large number cores (Choi et al., 2011). Furthermore, platforms can either be homogeneous, with symmetric or asymmetric multiprocessing; or heterogeneous, with different core types. This also substantially impacts in the way applications share data.

6 Introduction

Focusing on multi-core platforms, multiple solutions have been proposed exposing or not coherency between caches. One of the first examples of non-cache coherent approaches was provided by the experimental Intel Single-chip Cloud Computer (SCC) (Intel, 2010). This chip contained 24 tiles with two Pentium cores each, connected with a 4x6 2D-mesh, and a shared message passing buffer (MPB). Another platform exhibiting non-cache coherency between cores is the Kalray MPPA (Kalray, 2015). This platform consists of 16 clusters of 16 computing cores each, plus 32 cores that are dedicated to the management of the computing clusters, the I/O and the interconnect. Another architecture proposed by Intel is the Many Integrated Core architecture (MIC) (Intel, 2012). In this family, the Xeon Phi integrates 60 (Pentium-based) cores, but connected through a dual ring-bus. It features software-based coherency between caches. The Tilera (Tilera, 2012) architecture offers a different cache coherency solution. Each tile consists of a single core, with its own private cache and it is connected to the other tiles through several parallel NoCs (iMesh). On this platform, the tiles can be aggregated and form separate domains, with separate cache-coherent areas. The Epiphany platform (Adapteva, 2012) presents a similar organisation.

Recent architectures influence the way applications should be implemented in order to fully exploit the parallel computing power provided by these platforms. A promising candidate to this implementation paradigm is the thread-level parallel programming approach. By using this implementation methodology, the concurrency model of the tasks is prone to simultaneous requests of tasks running on different cores to shared resources, such as the main memory. Hence, the adopted synchronisation mechanism to manage the access to the shared resources and thus solve conflicts among transactions must be sharp, precise and well thought.

In the arena of admissible solutions, we adopt an STM-based approach as STM provides all the features to help us benefiting from the advantages of a concurrent programming paradigm, while limiting their potential disadvantages. More precisely, STM has proven to scale well with an increase of the number of cores available on a single processor chip (Dragojević et al., 2011). It delivers a higher throughput in comparison to coarse-grained locks and does not increase design complexity as compared to fine-grained locks (Rossbach et al., 2010). Last but not least, it is worth noticing that STM-based approaches present very good performances in terms of transaction abort ratio for systems with a low ratio of context switching during the execution of the transactions and with a predominance of (1) read-only transactions; and (2) transactions with a short execution time (Maldonado et al., 2010).

In this context, i.e., opting for an STM-based approach, the programmer writes sequential code as usual, but he has to specify through annotations the portions of the code that are to be executed as transactions. Although many optimisation techniques can be applied at the moment of breaking the ties between multiple transactions in conflicts (either a *read-write* or a *write-write* conflict), the role of the contention policy is to guarantee a meaningful and efficient serialisation of the access of the contending transactions to the shared resource. In this process, one transaction will always be granted the access, and thus the right to execute and commit, while the other contending transactions will be fated to abort, and consequently, will be deemed to repeat. The synchronisation details are seamlessly handled by an underlying mechanism that maintains the

consistency of the shared data objects located at the transactional memory.

In the parallel computing domain, the focus of STM-based approaches is limited to the system throughput, i.e., the number of commit per time unit. Here, the contention management policy is designed in such a manner that livelocks are avoided and starvation (i.e., any transaction constantly being aborted by the contenders) is minimized.

In the real-time systems domain, in addition to ensure that every transaction will eventually commit as this is the case in the parallel computing domain, the timing requirements of every task must also be satisfied. This means that we must also pay a special attention to the time by which every commit occurs. Consequently, when designing an STM-based approach for real-time systems, we must have two objectives in mind: (1) guarantee that the number of aborts of every transaction is upper-bounded and (2) make sure that the deadline of every task is met. To this end, a sound and convincing schedulability analysis must be conducted. This is one of the main contributions of this work.

## 1.3 Main thesis preposition

Considering the context presented in Section 1.2, the main objective of this thesis is to support the use of Software Transactional Memory in real-time embedded systems. The central preposition of this dissertation is:

The use of software transactional memory improves the composability of applications for multi-core embedded systems with real-time requirements.

This can be accomplished by designing a contention management policy for the execution and management of the transactions, associated to a scheduling algorithm for the execution of the tasks. These two components carefully developed and put together will result in a very limited number of aborts for every transaction as a guarantee of the timing requirements of every task. The adopted programming model to go along with these components will also need to be augmented with the required mechanisms to enable the correct use of this type of data sharing approach.

#### 1.4 Thesis contributions

Considering the previous main thesis preposition, the main contributions of this work are as follows:

C1: Design and implementation of a fair and predictable contention management algorithm.

The contention management policy for real-time applications (FIFO-CRT) proposed in this thesis serialises the transactions in such a manner that their timing attributes are considered. Unlike in lock-based synchronisation where a job suspends its execution while the desired resource is not free (thus yielding the processor to other ready tasks), here, a job holds the processor during the time it attempts to commit the transaction in execution. The

8 Introduction

designed policy provides a fair opportunity to commit to every transaction and is agnostic to the underlying task scheduling policy. In addition, it avoids deadlocks by making it possible for a later released transaction to abort an older released and preempted transaction. Along this line, we propose a set of rules on the scheduler associated to FIFO-CRT so as to prevent multiple simultaneous active transactions on each core, as this would result in an improvement of the responsiveness for each task.

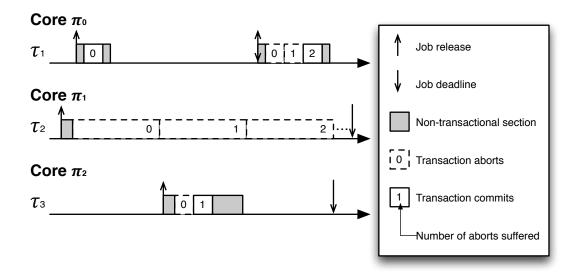

#### **C2:** *Design, implementation and analysis of three scheduling algorithms.*

Associated to the FIFO-CRT policy, we designed and analysed three fully-partitioned scheduling algorithms, denoted as Non-Preemptive Until Commit (NPUC), Non-Preemtive During Attempt (NPDA) and Stack Resource Protocol for Transactional Memory (SRPTM). These three scheduling algorithms are based on the classical Partitioned EDF (P-EDF) scheduler. Specifically, they take the same scheduling decisions as P-EDF when there is no transaction in progress; otherwise the scheduling decisions are adjusted accordingly by following predefined sets of metrics. This results in at most one active transaction per core, thus improving the predictability of the FIFO-CRT policy.

In addition, we implemented these three scheduling algorithms together with FIFO-CRT on a multi-core based computer hosting a PREEMPT-RT-patched Linux kernel version and tested with a large group of synthetic task sets.

#### C3: Specification of the language support in Ada.

The use of transactional code must be as transparent as possible for the programmer. Based on previous work on transactions for fault-tolerant systems, we propose in this thesis a syntax for the Ada programming language to support software transactional memory for concurrent real-time applications.

#### 1.5 Outline

This thesis is structured as follows.

Chapter 2 (Background on real-time embedded systems) provides an insight on the state-of-the-art on real-time embedded systems and real-time scheduling. Chapter 3 (Background on synchronisation mechanisms) presents an overview of synchronisation mechanisms for architectures based on multi-processor systems. Chapter 4 (System model) sets the system model and the assumptions adopted in this manuscript. It introduces all the parameters that will be used throughout this research work by distinguishing between three levels of abstraction, namely: the task specifications, the platform and scheduler specifications, and finally the STM specifications.

Chapter 5 (FIFO-CRT: a predictable STM contention management) formalises the FIFO-based contention management algorithm, referred to as First-In-First-Out Contention manager for Real-Time systems (FIFO-CRT), designed to provide predictability and prevent transaction starvation.

1.5 Outline

Chapter 6 (Scheduling tasks and transactions under FIFO-CRT) presents three scheduling policies – named (1) Non-Preemptive Until Commit (NPUC); (2) Non-Preemptive During Attempt (NPDA); and (3) SRP for Software Transactional Memory (SRPTM) – to address specific issues that impact on the predictability of FIFO-CRT. Chapter 7 (Schedulability analysis of tasks under NPDA, NPUC and SRPTM) reports on the schedulability analyses associated to these scheduling policies.

Chapter 8 (Evaluation) presents the simulation testbed that has been developed to compare the performance of our STM-based approaches (i.e. the FIFO-CRT contention manager associated to NPUC, NPDA and SRPTM scheduling policies) against the state-of-the-art lock-based synchronisation mechanism named Flexible Multiprocessor Locking Protocol (FMLP). This performance comparison is conducted by using the throughput of atomic sections executed by concurrent tasks and the number of deadline misses as the main metrics and a qualitative evaluation between all these approaches is also proposed. In order to analyse the performance of our synchronisation approaches and the precision of the theoretical analyses from a practical viewpoint, we implemented a minimalistic STM system with the FIFO-CRT contention manager as a Linux user space service, and the three scheduling policies in the Linux kernel. The results of these experiments are presented in Chapter 9 (Implementation).

Chapter 10 (Conclusions) summarises the contributions of this work and provides future research directions that can build upon the results of this thesis.

Appendix A (Ada language support for transactions) elaborates on the specifications of the programming language mechanisms that we proposed to support the execution of transactions. To this end, we discuss how the syntax of the Ada programming language can be adapted so as to support STM transactions.

Finally, Appendix B (Bounded-memory multi-version STM for real-time systems) elaborates on how to execute read-only transactions free of aborts by tuning a multi-version STM. Unlike for general-purpose STM systems, the timing characteristics of real-time task sets offer the opportunity to determine the exact number of versions for each data object.

10 Introduction

# Chapter 2

# Background on real-time embedded systems

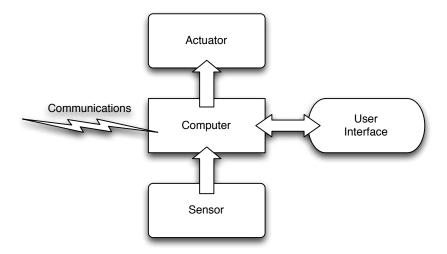

An *embedded system* is a computer that interacts with its surrounding physical elements and is implemented for a specific purpose. Figure 2.1 illustrates the general building blocks of such a system<sup>1</sup>. An embedded system is meant to control a larger system in which the computer is inserted. It perceives and receives stimuli from the physical system through *sensors*, and makes use of *actuators* to modify the state of the controlled physical system. Embedded systems have an innumerable range of applications such as smartphones, vehicle electronic stability control, industrial process control or rocket guidance systems, to name a few. Unlike a general purpose computer that performs a wide range of unforeseen tasks, the hardware design of an embedded system addresses the requested functionality. As such, the hardware components are selected to fit the requirements in order to reduce the final unit cost, which is very important in large scale applications or in mass-production commercial products.

Most embedded systems have to deal with real-time constraints and are as such called *real-time embedded systems*. These special embedded systems are those in which the correctness of the system depends not only on the correctness of the logical results of the computations, but also on the time at which these results are produced (Stankovic, 1988). Traditionally, the functionality of a real-time system is divided into less complex parts that are referred to as *tasks*. A task is a sub-program that is responsible of a particular part of the system. It is characterised by specific timing requirements and can be invoked recurrently for a potentially infinite number of times. Every invocation is also known as a *job* of the task. Each job is triggered either by time or an event, and must complete within a given time frame, defined by a deadline. The consequences of a job not being able to finish within the time frame depend on the criticality of the task. In some cases, violating the temporal constraints can lead to catastrophic consequences. For example,

<sup>&</sup>lt;sup>1</sup>An embedded system communicates with other systems via dedicated *communication* technologies, and with a human operator via a *user interface*.

Figure 2.1: Typical embedded system building blocks.

if the thrust reverser systems accidentally take too long to activate after an aircraft touches the ground, the aircraft may not decelerate rapidly enough to avoid overrunning the runway. In other cases, the consequences can be experienced as a degradation in the quality of service, without posing any catastrophic risk. For example, if a runner's wrist GPS watch occasionally loses the fix on satellites, it may be annoying (the runner may temporarily not know his pace) but it will not have harmful consequences on the runner's integrity. Therefore, there is a special concern on how to schedule the set of tasks with sufficient resources to ensure that critical deadlines are met. A schedulabilty analysis allows to determine before runtime if a given scheduling algorithm will be able to meet the timing requirements of all the tasks on a target computing platform. This analysis must be rigorous for (critical) systems, ensuring that no temporal constrains will be violated; and must ensure that the timing requirements will be observed such that the quality-of-service provided by the system is within the expected for systems that are not critical.

This chapter presents an overview of the real-time scheduling of tasks for multi-core systems, and discusses relevant works published on this topic.

# 2.1 Modelling real-time systems

We recall that a real-time system distinguishes itself by the temporal constraints that augment the functional requirements of its constituent tasks. This section describes how the functionality and workload of a real-time application is modelled by the concepts of *task* and *job*, according to the classic periodic/sporadic task model, as formalised by Mok (1983).

**Definition 1** (Task). A *task* is an executable entity of workload that defines one part of the functionality provided by the system. A task is denoted as  $\tau_i$ , where  $i \in \mathbb{N}^+$  is the task index.

Each task  $\tau_i$  is usually characterised by three parameters —  $C_i$ ,  $D_i$  and  $T_i$  — which are given with the following interpretation:

- a worst case execution time (WCET)  $C_i$ . This parameter defines the maximum processor time without interruption required by any job of task  $\tau_i$ .

- a relative deadline  $D_i$ . This parameter defines the maximum time window required by each job of task  $\tau_i$  to complete its execution.

- an *activation interval*  $T_i$ . This parameter defines the time span between two consecutive jobs of task  $\tau_i$ . If  $T_i$  is constant, i.e., every job is released as soon as it is legally permitted to do so, then  $\tau_i$  is called *periodic*; else if  $T_i$  is a minimum, then  $\tau_i$  is called *sporadic*; otherwise,  $\tau_i$  is called *aperiodic*.

Each task  $\tau_i$  is further characterised by the relationship between its relative deadline  $D_i$  and its activation interval (also referred to as period)  $T_i$ .

- Implicit deadlines. Task  $\tau_i$  is referred to as implicit deadline if  $D_i = T_i$ .

- Constrained deadlines. Task  $\tau_i$  is referred to as constrained deadline if  $D_i \leq T_i$ .

- Arbitrary deadlines. Task  $\tau_i$  is referred to as arbitrary deadline if  $D_i$  and  $T_i$  are independent.

**Definition 2** (Task utilisation). The *task utilisation* is the maximum ratio of the processor capacity used by the task. For task  $\tau_i$ , it is denoted as  $U_i$  and is formally defined as  $U_i = C_i/T_i$ .

**Definition 3** (Task set). The *task set* is the collection of all tasks that compose the system under analysis. A task set which consists of n tasks is denoted as  $\tau$  and defined as  $\tau = {\tau_1, \ldots, \tau_n}$ .

**Definition 4** (Task set utilisation). The *task set utilisation* is the maximum ratio of the processor capacity used by the whole task set. For the task set  $\tau$ , it is denoted as  $U_{\tau}$  and is formally defined as the sum of the utilisation of all individual task utilisations, i.e.,  $U_{\tau} = \sum_{i=1}^{n} U_{i}$ .

#### This research considers sporadic implicit deadline task sets.

The sporadic implicit deadline task model of execution assumes that every task consists of a potentially infinite sequence of jobs such that (i) every two consecutive jobs are separated by at least the task's period and (ii) the relative deadline of the task is equal to the task's period, i.e., the execution of every job must finish before the following job is released. From now onward, we refer to the  $j^{th}$  job of task  $\tau_i$  as  $\tau_{i,j}$ . Each job  $\tau_{i,j}$  is characterised by a set of timing attributes —  $r_{i,j}$ ,  $s_{i,j}$ ,  $d_{i,j}$ ,  $f_{i,j}$ ,  $rt_{i,j}$  — that are relative to the instant at which the job is released.

- The *release time*  $r_{i,j}$ . This attribute corresponds to the time at which the job is released and becomes ready for execution.

- The *start time*  $s_{i,j}$ . This attribute corresponds to the time at which the job actually starts executing. The job may not be scheduled upon its release, so  $s_{i,j} \ge r_{i,j}$ .

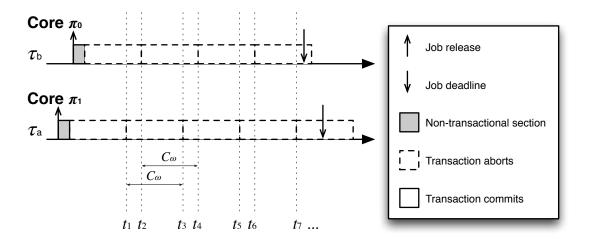

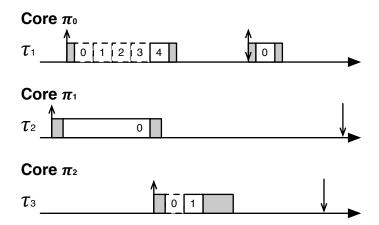

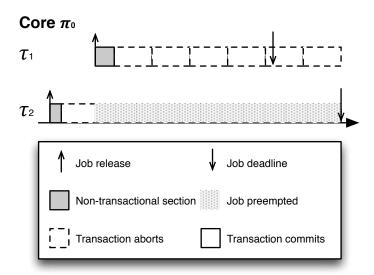

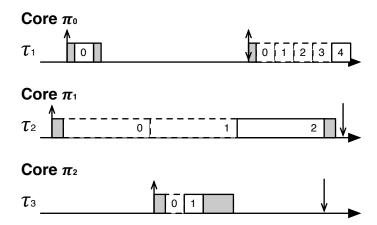

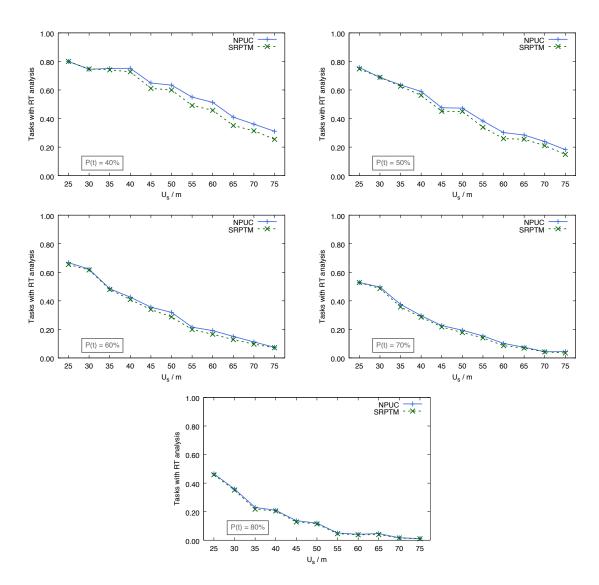

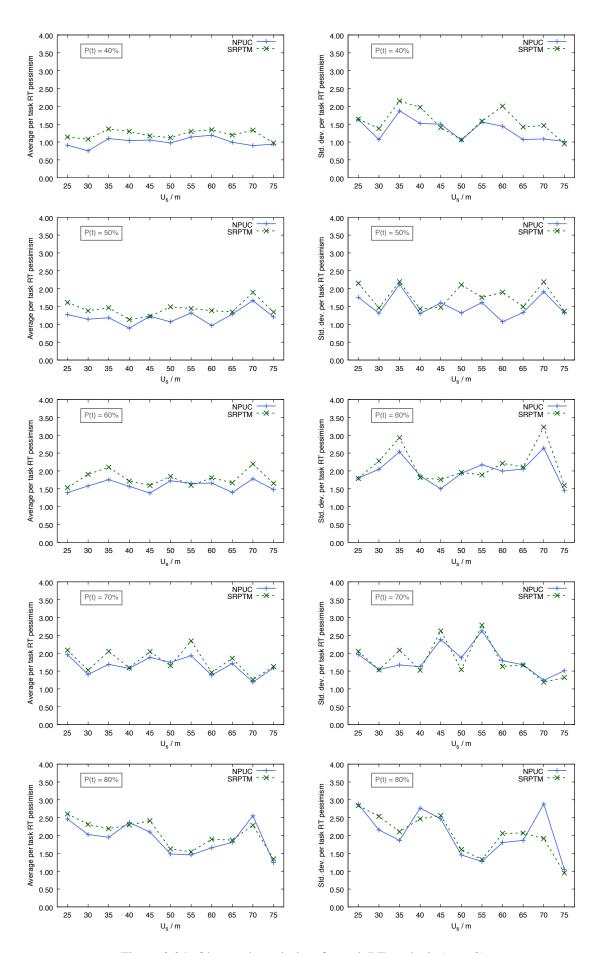

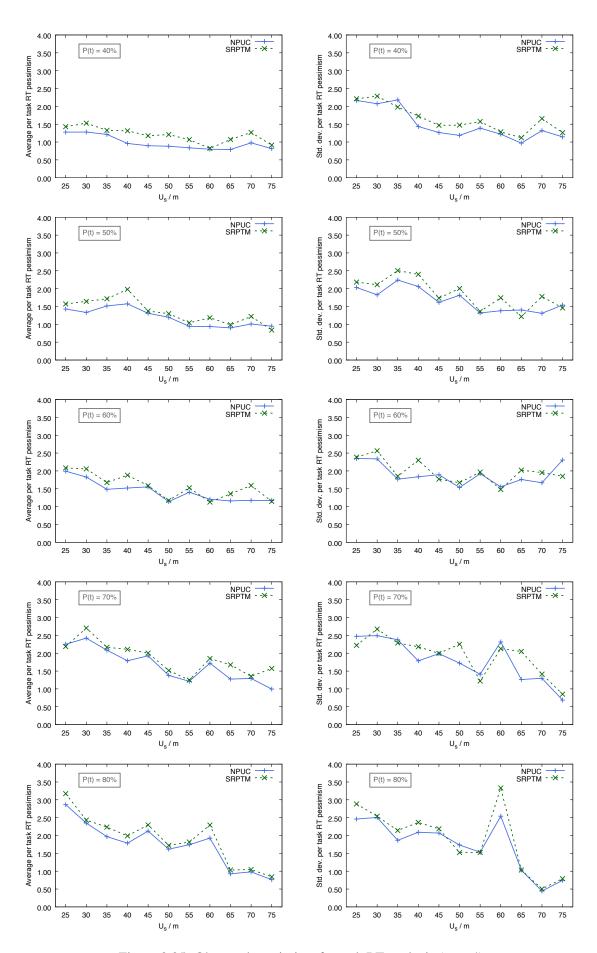

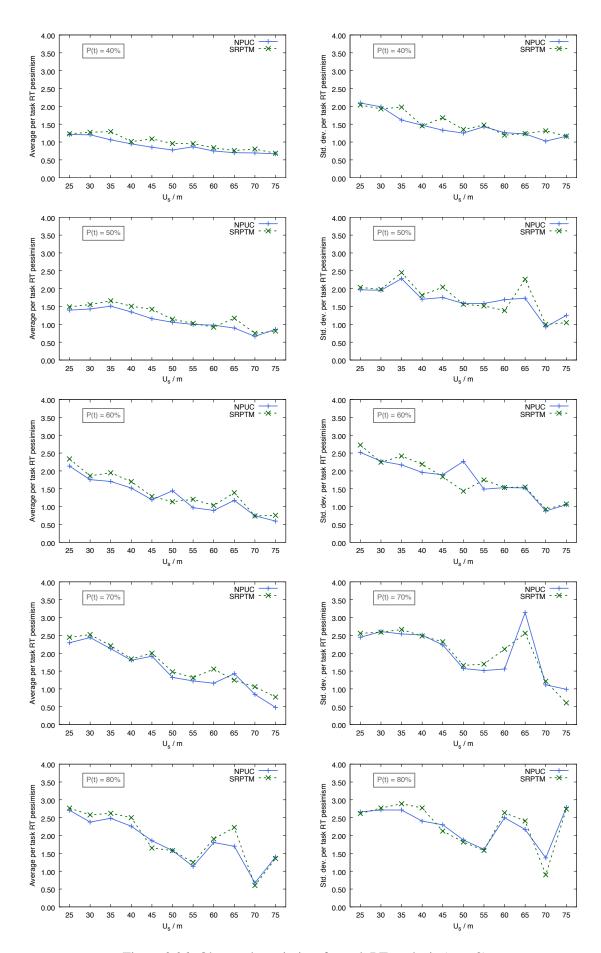

- The absolute deadline  $d_{i,j}$ . This attribute defines the time by which the job must have completed its execution. Formally,  $d_{i,j} = r_{i,j} + D_i$ .