# **Journal Paper**

# An industrial view on the common academic understanding of mixed-criticality systems

Alexandre Esper Geoffrey Nelissen Vincent Nélis Eduardo Tovar

CISTER-TR-180810

2018/07

# An industrial view on the common academic understanding of mixed-criticality systems

# Alexandre Esper, Geoffrey Nelissen, Vincent Nélis, Eduardo Tovar

\*CISTER Research Centre Polytechnic Institute of Porto (ISEP-IPP) Rua Dr. António Bernardino de Almeida, 431 4200-072 Porto Portugal Tel.: +351.22.8340509, Fax: +351.22.8321159 E-mail: alexandre.esper@altran.com, grrpn@isep.ipp.pt, nelis@isep.ipp.pt, emt@isep.ipp.pt http://www.cister.isep.ipp.pt

# Abstract

With the rapid evolution of commercial hardware platforms, in most application domains, the industry has shown a growing interest in integrating and running independently-developed applications of different 1ccriticalities 1d in the same multi-core platform, with the objective of improving the performance/cost ratio of the system. Such integrated systems are commonly referred to as mixed-criticality systems (MCS). Most of the MCS-related research published in the state-of-the-art cite the safety-related standards associated to each application domain (e.g. aeronautics, space, railway, automotive). However, those standards are not, in most cases, freely available, and do not always clearly and explicitly specify the requirements for mixed-criticality systems. This paper addresses the important challenge of presenting the relevant information available in some of the safety-related standards, such that the mixed-criticality concept is understood from an industrialist 19s perspective. In addition, the paper evaluates state-of-the-art mixed-criticality real-time scheduling models and algorithms against the safety-related standards.

# An industrial view on the common academic understanding of mixed-criticality systems

Alexandre Esper<sup>1</sup> · Geoffrey Nelissen<sup>2</sup> · Vincent Nélis<sup>2</sup> · Eduardo Tovar<sup>2</sup>

Published online: 10 May 2018 © Springer Science+Business Media, LLC, part of Springer Nature 2018

**Abstract** With the rapid evolution of commercial hardware platforms, in most application domains, the industry has shown a growing interest in integrating and running independently-developed applications of different "criticalities" in the same multicore platform, with the objective of improving the performance/cost ratio of the system. Such integrated systems are commonly referred to as mixed-criticality systems (MCS). Most of the MCS-related research published in the state-of-the-art cite the safety-related standards associated to each application domain (e.g. aeronautics, space, railway, automotive). However, those standards are not, in most cases, freely available, and do not always clearly and explicitly specify the requirements for mixed-criticality systems. This paper addresses the important challenge of presenting the relevant information available in some of the safety-related standards, such that the mixed-criticality concept is understood from an industrialist's perspective. In addition, the paper evaluates state-of-the-art mixed-criticality real-time scheduling models and algorithms against the safety-related standards.

Keywords Mixed-criticality · Safety-related standards · Real-time scheduling

Alexandre Esper aresper@criticalsoftware.com

Geoffrey Nelissen grrpn@isep.ipp.pt

> Vincent Nélis nelis@isep.ipp.pt

Eduardo Tovar emt@isep.ipp.pt

- <sup>1</sup> Critical Software S.A., Porto, Portugal

- <sup>2</sup> CISTER/INESC-TEC, ISEP, Porto, Portugal

#### 1 Introduction

In the last decade and in most application domains, the industry has shown a growing interest in developing methods and tools to implement, deploy, validate, and certify independently-developed applications of different "criticalities" in the same multi-core platform, with the evident objective of improving the performance/cost ratio of the system. Such integrated systems are commonly referred to as mixed-criticality systems (MCS). All over the world, the industrial interest in MCS has manifested itself in the form of important investments placed into R&D projects and academics since long time started to manifest their interest as well. The research community that focuses on the real-time scheduling theory has actively taken part in these efforts regarding MCS. Their base application model has quickly developed into a mixed-criticality (MC) task model that is today well-accepted and used in most research works on the subject. This model is based on the model proposed by Vestal (2007) and in this paper we will focus on that specific model and its related work. This new MC task model is in essence the result of combining the standard hard real-time requirements (studied by the real-time research community since the 70s) with the notion of "criticality" of execution. When transposed into the industrial world, the applications that correspond the best to that MC model and its combined requirements are those in which a part of the core functionality is delivered by safety-critical components.

The introduction of new constraints and requirements into the theoretical models has unexpectedly unveiled a brand new research landscape. Into this virgin research field some of the seminal results in scheduling theory had to be restated and revalidated, and an entire body of knowledge was to be rebuilt. The popularity of MCS immediately soared up in the real-time research community, which has been evidenced by the sudden emergence of tracks, sessions, and workshops that are now entirely dedicated to MCS in most of the flagship conferences on real-time systems.

Since its conception, the MC model has been gradually gaining sophistication by incorporating multiple levels of criticality or probabilistic WCET estimates to mention a couple of examples. Each transformation of the model has been motivated and justified as a mean to better cope with the requirements of MCS. However, most of the safety-related standards are not freely available, and still, the real-time community is confronted with the challenge of proposing solutions with certification potential to current industrial problems, i.e., solutions that are compliant with the safety-related industrial standards requirements and constraints. Considering this challenge, the main contributions of this paper are: (i) a practical survey and interpretation of some of the main safety-related industrial standards, thus complementing the academic MCS survey by Burns and Davis (2013); (ii) the identification of key requirements that must be taken into consideration when designing MCS solutions with certification potentials.

It is important to highlight that the objective of this work is not to judge all the theoretical contributions on MCS proposed so far, but simply to provide the minimum background material for those motivated to propose solutions to current industrial problems and challenges of the safety-critical industry. It is our hope that theoretical works can benefit from the contribution of this paper, in the sense that they can re-

think and strengthen their assumptions toward more robust models with certification potential.

In our discussions, we refer to recommendations and requirements for the design of safety-critical applications using the three following standards: the IEC61508 [generic electrical and/or electronic and/or programmable electronic (E/E/PE)] (IEC61508 2010), the ISO26262 (automotive domain) (ISO26262 2011) and the DO-178C (aeronautics domain) (DO-178C 2011); those three standards being the most commonly cited in the real-time research literature on MCS.

An important aspect that must be highlighted with respect to the focus of this work is that it does not aim at covering or debating hardware configurations, e.g., multicore versus single-core. Nevertheless, with the current trend of evolution of hardware platforms toward multi-cores, mainly due to the need of sharing resources to improve on SWaP (size, weight, and power), our work inevitably biases its attention towards those architectures. Note however that all the concepts discussed hereinafter are also applicable to single-core hardware platforms.

**Organisation of the paper** In order to provide the reader with sufficient background information, we start in Sect. 2 with an overview of the safety assessment process as required by the standards for the development of safety-critical systems. That section briefly explains how in practice the safety requirements are derived and how the development assurance levels (DALs) are assigned to the system safety functions. With this background, we introduce in Sect. 3 the concept of a mixed-criticality system (MCS for short). In Sect. 4, we summarize the most important architectural considerations and requirements from the three above mentioned safety-related industrial standards, with respect to the development of MCS. We conclude the "industry-oriented" part of the paper by presenting in Sect. 5 the industrial solutions that prevail in the aeronautic and automotive application domains to design mixed-criticality systems in accordance with their domain-specific requirements. We then move to the "academy-oriented" part of the paper. We start in Sect. 6 by discussing the Vestal model, the theoretical model of MCS most commonly found in the academic literature. We focus on Vestals model because of its wide acceptance in the real-time system academic community to model MCS. We use Sect. 6 to highlight key aspects of that model that are not fully compliant with the safety-related industrial standards. As a preliminary step towards setting a model that is compliant with the safety-related standards, we list in Sect. 7 some key requirements that *must* be captured and taken into consideration in the model. Then in Sect. 8 we discuss some of the academic solutions that may be compliant with those requirements. Finally, the paper is concluded in Sect. 9.

#### 2 System design and development assurance process

In order to understand the concept of MCS from the industrial perspective, it is necessary to firstly understand that the safety-related industrial standards do not explicitly specify requirements for MCS, but they do specify stringent requirements that must be met to ensure the *safety* of the system. Secondly, it is necessary to understand that "criticality" is a generic term commonly adopted to designate the type of systems that perform safety critical functions, i.e., functions that in case of failure can potentially lead to e.g., injuries, death or damage to properties or to the environment. In the safety-related standards, different types of more specific terminologies are use to designate those functions, as well as their different levels of "criticalities", which depend on the severity of the consequences and the probability of occurrence of their failures. The generic concept of "criticality" is therefore used to determine the level of rigour required to develop those safety critical functions in such a way that the risk of failure can be brought to an acceptable level. Therefore, to avoid generalizations of terminology that may potentially lead to misinterpretation of the safety-related standards requirements, it is of uttermost importance to precisely understand the industrial process for assigning those "criticality levels" to those functions, and why these functions must be isolated from each other to be able to safely coexist in the same platform (i.e., an essential requirement for implementing an MCS). To achieve that goal, we summarize in this section, as an example, the system design and development process adopted in the aeronautic domain for assigning those "criticality levels", more specifically known as development assurance levels (DALs).<sup>1</sup>

During a typical development life-cycle of a safety-critical system, the behavior and characteristics that are expected from the system are expressed in the form of a list of requirements. Those are developed based not only on the system operational requirements (what the system is expected to do), but also considering non-functional properties related to safety, security and performance, including timing and energy constraints. In order to ensure the safety properties of a safety-critical system, a *system safety assessment process* must be carried out as part of the development life-cycle to determine and categorize the failure conditions of the system (e.g. through a hazard analysis). As a result of the system safety assessment process, safety-related requirements are derived, which may include functional, integrity, dependability requirements and design constraints. These requirements are then allocated to hardware and software components, thereby specifying the mechanisms required to prevent a fault occurring or to mitigate their effects and avoid the propagation of failures.

To help understand the safety-critical system development life-cycle, we provide below an overview of the safety assessment process commonly defined by the standards, e.g., ARP4761 (1996) and ARP4754 (ARP4761A 1996). We hence briefly explain how, in practice, the *development assurance levels* (DALs) are assigned to the system safety functions. Note however, that even though the fundamental concepts are in essence the same across most safety-related standards, the approaches adopted in each case varies, which makes the description of a general cross-domain safety assessment process not a straightforward task.

#### 2.1 General safety assessment process

The safety assessment process starts *at the system level* with a hazard analysis. This technique identifies the system hazards and assesses their severity (according to the domain specific severity scale) by taking into account the operational environment. After that, a fault analysis is performed to identify the failure conditions that can trigger

<sup>&</sup>lt;sup>1</sup> Note that in Sect. 2.2 other terminologies used in other domains will be presented.

the identified hazards. The most known fault-analysis techniques that are used across domains are the Fault Tree Analysis (FTA) (see Sect. 4.1 of ARP4761 (1996)) and the Failure Modes and Effects Analysis (FMEA)(see Sect. 4.2 of ARP4761 (1996)).

FTA is a top-down analysis technique that proceeds down through successively more detailed lower levels of the design. It facilitates the safety assessment process in the sense that it identifies only the failure events that combined (or individually) can lead to the occurrence of the undesired top level event. If the failure rates of the basic events are known, the probability of occurrence of the top level event can be quantified.

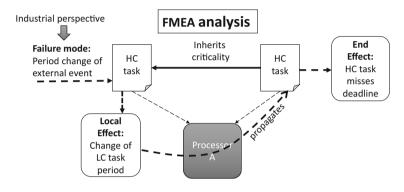

The FMEA on the other hand is a systematic bottom-up technique used to identify the failure modes of a system, function or component, and to determine their effects to the system upper levels. Contrary to the FTA, the FMEA addresses only failure effects that result from single failures.

FTA and FMEA are complementary techniques. Section 3.2 of ARP4761 provides a good overview of how these two techniques relate to each other and to the hazard analysis. After the identification of the failure conditions in the hazard analysis, the FTA can be applied to determine what single failures or combinations of failures can exist (or not) at the lower system levels that might cause each failure condition. The fault tree can then be complemented by the FMEA to ensure that all significant effects are identified as basic events (lowest level) of the tree. The FTA basic events can also get their failure rates from the FMEA. A lower level system item (e.g., component) contributes to the failure condition if it appears in one of the tree branches leading to the failure condition. A DAL is then assigned to the item according to the severity level of the worst failure condition that it contributes to.

Safety assessment also plays an important role at the software level, especially in the context of MCS, where the isolation of applications of different criticalities requires special attention. The inclusion of software errors in a qualitative manner in the safety analysis shows their contribution to the various failure conditions and can provide valuable information on deriving the DAL. The software safety assessment can also identify the specific safety related requirements for software such as containment boundary definitions, partitioning strategies, and specific verification strategies. Considering this, the criticalities of the applications need to be demonstrated by means of a fault analysis (either FTA, FMEA or both), which allows to assess the contribution of their software failures to the identified system hazards. However, when applying fault analysis techniques to software, the relationship between the top level hazards and software hazards or feared events (software specific anomalous behaviours) must be clearly determined. It is important to explicitly identify how a failure of a certain software function can affect other software and system functions, and whether they can potentially contribute or not to a system hazard.

The software hazard analysis is a top-down technique that makes recommendations to eliminate or control software hazards and relates the hazards to the interfaces between the software and the system. Software hazard analysis should ensure that the software does not interfere with the objectives and correct operation of the system. In the case where interference cannot be totally avoided the software hazard analysis must also evaluate and make recommendations to mitigate how the software can hinder the objective or operation of the system.

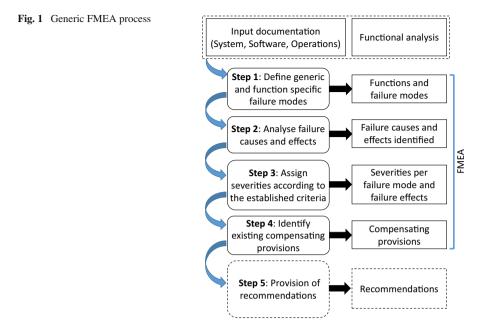

As explained in Sects. 4.1.2 and 4.2 of ARP4761, both FTA and FMEA can be used to perform a qualitative analysis of complex systems such as MCS, hence supporting the definition of mitigation measures, which may include hardware or software mechanisms and/or the inclusion of specific verification activities in the development process. We briefly describe the software fault analysis process using FMEA as an example. Figure 1 summarises the generic software FMEA process. The first step consists in performing a functional analysis, i.e., a listing and description of the software functions (rather than the items used in their implementation), and to define the generic failure modes to be applied to each function of each software component. The generic failure modes typically include incorrect execution, non-execution, or late execution of a software function. Therefore, based on the input documentation and on the previously identified software functions derived from the software requirements, the generic failure modes are mapped to the functions of each software component and the component's specific failure modes are then derived. Step 2 consists in analysing the component possible failure causes that can trigger the identified failure modes and on identifying the end effects of the failure mode to the system (possible failure propagation). During Step 3 severity categories (i.e., how bad is the consequence for the system) are assigned to every single failure mode. The severity of the consequences of the failure modes assigned in accordance with the severity assignment criteria defined specifically for the system being developed. Step 4 is the identification of existing compensating provisions that can either

- 1. circumvent or mitigate the effect of the failure,

- 2. control or deactivate product items to halt the generation/propagation of failure effects, or

🖄 Springer

3. activate backup or standby components to (at least partially) recover from the failure.

Generally speaking, design compensating provisions include:

- Redundant components or alternative modes of operation that allow continued and safe operation;

- Safety or relief feature (hardware or software) that allows effective operation or limit the failure effects.

Once the severity categories have been assigned to the failure modes and consequently to the respective software components, recommendations can be provided with the objective of reducing the risk associated with the potential critical faults identified (e.g. by increasing the amount and rigour of verification and validation activities).

#### 2.2 Development assurance level

The software DAL establishes the necessary rigour of the development and of the verification and validation (V&V) activities that need to be performed on the software, in accordance with the adopted standard. The higher the DAL of a software, the higher the number of assurance activities that need to be performed, thus also increasing considerably the costs of its development. The process for the development of safety-critical software, which assures the software safety and dependability properties at a certain DAL is defined in several standards across several application domains (for instance, see Sect. 5.6 of ARP4761A (1996)). Typically, the DALs are divided into 4 or 5 levels, related to the categories of severity of a failure adopted by the standard. For instance, under the DO-178C (DO-178C 2011) standard (in the avionic domain), five severity categories are defined. These five categories are:

- 1. Catastrophic failures that result in multiple fatalities or the loss of the airplane.

- 2. **Hazardous** failures that result in serious or fatal injury to a relatively small number of occupants.

- 3. **Major** failures that reduce the capability of the airplane or the ability of the crew to cope with adverse operating conditions.

- 4. Minor failures that do not significantly reduce the airplane safety.

- 5. No safety effect failures that have no effect on safety.

The software DALs are then assigned depending on the severity category assigned to the failure(s) that may be caused by the analysed software component. Specifically, there are five levels defined as level A/B/C/D/E which are respectively assigned to software components (or modules) whose anomalous behaviour would lead to a system failure of catastrophic, hazardous, major, minor or negligible consequences. That is, a software that can potentially contribute to a catastrophic system failure shall be developed according to DAL-A requirements.

So far we have used DO-178C as reference for explaining the concept of development assurance level (DAL). However, IEC61508 and ISO26262 use different terminologies for describing the development process of a safety-critical or safetyrelated system, although the fundamental concepts are in essence the same.

IEC61508 defines the concept of system safety function. System safety functions are implemented by a safety-related system whose purpose is to achieve or maintain a safe state for the equipment under control (e.g. car engine) when a specific hazardous event occur. Associated to the system safety functions, the concept of safety integrity is defined, which refers to the probability of a safety-related system to satisfactorily perform the required safety functions under all the state conditions within a specified period. There are four *safety integrity levels* (SIL). The higher the safety integrity level of the safety function, the lower the probability that the safety-related system that executes that function will fail. Software SILs are used as the basis for specifying the safety integrity requirements of the system safety functions implemented by safetyrelated software. Although the SIL is composed of four levels, the IEC61508 does not explicitly define the failure severity categories and their association with the SIL. Only examples are provided that are not fully detailed. For instance, in Table C.1 of IEC61508-5 (IEC61508 2010), the following failure severity category levels are provided: catastrophic, critical, marginal and negligible. It is up to the system designers to define and detail those categories but it is important to note that the definition of those is based only on *qualitative* rather than quantitative measures. This note will be further discussed in Sect. 8.6.

ISO26262 derives from the generic IEC61508 and addresses the specificities of the automotive sector. ISO26262 defines the automotive safety integrity level (ASIL). Similarly to the SIL defined in IEC61508, the ASIL are composed of four levels, where D represents the most stringent and A represents the least stringent level in terms of requirements and safety measures (note that this is the exact opposite to the scale used by DO-178C). The higher the ASIL, the greater the needs to reduce the risk. Table 1 presents the risk matrix for the ASIL determination of hazardous events of automotive systems. It uses three parameters: "severity", "probability of exposure" and "controllability".<sup>2,3</sup> The severity defines the estimation of the extent of harm to one or more individuals that can occur in a potentially hazardous situation, the associated probability is the likelihood of the occurrence of harm, and the controllability is the ability to avoid a specified harm or damage through the timely reactions of the agents involved (e.g. the driver of the vehicle) possibly with support from external measures. Therefore, the ASILs explicitly consider one more parameter in comparison to the SILs, which is the ability to control failure effects. Note that, as it can be seen in Table 1, a high controllability (class C1) can often help reduce the ASIL of the components by 2 levels in comparison to the case where the controllability is almost inexistent (class C3).

#### 2.3 Distinction between safety-critical, mission-critical and non-critical systems

Based on the safety assessment process presented in the previous subsections for assigning the DAL or the SIL, it is important to make the distinction between safety-

$<sup>^2</sup>$  A detailed description of these 3 parameters are outside the scope of this work. Please refer to ISO26262 (2011) for further details.

<sup>&</sup>lt;sup>3</sup> In addition to the four ASILs, the class QM (quality management) denotes no requirement to comply with ISO26262 other than the project quality assurance requirements.

| Table 1   ASIL determination     for hazardous events (ISO26262     2011) | Severity class | Probability class | Controllability class |    |    |

|---------------------------------------------------------------------------|----------------|-------------------|-----------------------|----|----|

|                                                                           |                |                   | C1                    | C2 | C3 |

|                                                                           | S1             | E1                | QM                    | QM | QM |

|                                                                           |                | E2                | QM                    | QM | QM |

|                                                                           |                | E3                | QM                    | QM | А  |

|                                                                           |                | E4                | QM                    | А  | В  |

|                                                                           | S2             | E1                | QM                    | QM | QM |

|                                                                           |                | E2                | QM                    | QM | А  |

|                                                                           |                | E3                | QM                    | А  | В  |

|                                                                           |                | E4                | А                     | В  | С  |

|                                                                           | S3             | E1                | QM                    | QM | А  |

|                                                                           |                | E2                | QM                    | А  | В  |

|                                                                           |                | E3                | А                     | В  | С  |

| S severity class, E exposure, C controllability                           |                | E4                | В                     | С  | D  |

critical, mission-critical and non-critical systems. To grasp the difference between those, it is fundamental to understand the difference between the concepts of safety and dependability (reliability, availability and maintainability). A safety-critical system can be understood as a system that, in case of severe failures, can lead to, e.g., injuries or death of individuals or group of individuals, or severe damage to environment, in accordance to the safety assessment performed according to the project criteria, as explained in the previous subsections. Examples of those types of systems are: aeronautic, railway and automotive systems. On the other hand, there are certain types of systems where the safety assessment process can demonstrate that even in a worst case failure scenario, the worst consequence that can potentially occur is the loss of the system, without any threat to human integrity or the environment. Mission-critical systems are commonly developed, for instance, for the space industry (e.g., satellite systems). In this case, it will be the organization or business that owns the system that will suffer the consequences of the failure, such as considerable financial losses. Therefore, the reliability, availability and maintainability (RAM) properties become the key concern when designing mission-critical systems. As an example, the reader is invited to consult Table 6-1 of standard (ECSS-Q-ST-40C 2009), which defines how the severity of potential consequences of undesirable events shall be categorized, both in terms of safety and/or dependability. As explained in clause 6.4.1b of ECSS-Q-ST-40C (2009), an understanding of the criteria defined in Table 6-1 (ECSS-Q-ST-40C 2009) shall be agreed between customer and supplier. For example, satellites developed for the European Space Agency (ESA) are typically developed to criticality level B (similar to the aeronautic DAL-B), as defined in Table D-1 of ECSS-Q-ST-80C (2009). Finally, non-critical systems are those types of systems where, according to the project criteria, even in a worst case failure scenario, the consequences will be minor, thus not significantly impacting the nominal system operation.

#### 3 The notion of mixed-criticality systems

Considering the process presented in the previous section for assigning the DALs, the concept of mixed-criticality becomes straightforward to understand. A mixedcriticality system consists of applications of different DALs coexisting in the same system, sharing the same resources (potentially including the CPUs) but still preserving the safety characteristics of each individual application as required by the domain-specific safety-related standards. In addition, a MCS is first of all a critical system for which we want *simple* and *modular* designs. All safety-related standards in every application domain advocate the use of these principles in the design of such systems. These guidelines can be justified in a thousand ways, but in short, a simpler design guarantees a simpler conception phase and a simpler and thus less costly V&V, while modularity allows for better maintainability and easier upgradability.

The high-level process explained in the previous section for assessing the criticality of software systems is an important activity in the design of safety-critical systems, and consequently of mixed-critical systems. Based on the understanding of this process, one can conclude that there are two main solutions to reduce the criticality of a system component (i.e., to reduce the risk of severe failures):

- 1. Avoiding the propagation of faults between different components and in particular from low criticality components to higher criticality components;

- 2. Providing compensating provisions by adding effective mechanisms that could either prevent or mitigate the effects of a failure.

It also becomes clear that improving the reliability of the software, by reducing the risk of failures, is an essential step in the design of MCS.

Another important observation, considering the development assurance requirements derived from the risk assessment process described in the previous section, is that a certain system does not change its criticality during operation. Therefore, a mismatch in the interpretation of the concept of "system criticality" exists between the industrial standards and the academic papers, and is further discussed in Sect. 6.2. What happens in practice is that in the occurrence of a fault, the system may enter a different mode of operation, where less important functions can be dropped in benefit of the more important ones. This is related to the concept of graceful degradation, which will be discussed later in Sects. 4.2.4 and 6.5.

# 4 Requirements of safety-related industrial standards applicable to the development of MCS

After the introduction of the basic concepts, methodologies, and terminology for understanding and discussing MCS in Sects. 2 and 3, we summarize next key architectural considerations and requirements extracted from three safety-related industrial standards (IEC61508, DO-178C and ISO26262) that are deemed as most relevant for the design of MCS solutions with certification potential. We highlight the importance of this section since most of the safety-related standards are not freely available for the real-time community and even for industrialists it is very difficult to get access to a broad set of standards of several different domains.

#### 4.1 The DO-178C

The DO-178C standard describes a set of important techniques that can be applied during the design of avionics systems, which may prevent software failures and/or limit or circumvent their effects on the system functions. To achieve that goal, the system safety assessment process needs to demonstrate that the software components will execute with sufficient independence. This independence must be ensured at the functional level, i.e., during the specification of the high-level software requirements, and at the design level, e.g., definition of common design elements, languages, and tools. If sufficient independence between software components cannot be demonstrated (e.g., through partitioning), then those components will be viewed as a single software component when assigning the software DAL. This implies that the DAL assigned to the components will be the DAL associated with the highest failure severity category that those components can contribute to.

Under DO-178C, the following safety-related software design methods are discussed: partitioning, dissimilarity (or redundancy), and safety monitoring. Dissimilarity is a design technique also referred to as multi-version software, where two or more different software components that perform the same functions are developed independently (Sect. 2.4.2 of DO-178C). It intends to avoid common sources of errors to contaminate the different versions of the same component. However, in the industry this technique is rarely applied due to its typically excessive cost and is thus not further discussed in this paper. Partitioning and safety monitoring as described in DO-178C are discussed in details below.

#### 4.1.1 Partitioning

Similarly to IEC61508, DO-178C presents partitioning as one of the most important design instruments to safety-critical systems. The decision regarding the partitioning approach to be applied to a project must be taken during early phases of the software development life-cycle (Sect. 2.4.1 of DO-178C) and must address the following aspects: (i) the extent and scope of interactions that will be allowed between the partitioned components, (ii) how to isolate the components from each other, i.e., which protection strategy will be adopted (e.g through hardware functions or a combination of hardware and software).

Regardless of the adopted approach, DO-178C establishes five requirements for ensuring partitioning between the partitioned software components. The first requirement states that the code, input/output, or data storage areas of a software component cannot be contaminated by another software component that belongs to a different partition. The second requirement refers to the consumption of shared CPU time. A partitioned software component is only allowed to consume CPU time during its scheduled period of execution. The third requirement is related to hardware failures within a partition. Each partition should be able to contain the fault, i.e., a fault should not be able to propagate to the other partitions and hence cause failure of software components in those other partitions. The fourth requirement discusses the DAL level of the software application that provides the partitioning functionality to the system. This requirement states that the software that implements the partitioning functionality should have the same or higher DAL than the highest DAL of the software components assigned to any of the provided partitions. If the partitioning functionality is provided via hardware, the fifth requirement requires that a safety assessment must be performed on that hardware to ensure that in case of failure it will not cause failures on the software partitions and consequently affect the system safety.

#### 4.1.2 Safety monitoring

As already mentioned in Sect. 4.2.2, safety monitoring (Sect. 2.4.3 of DO-178C) is a technique that allows the protection against specific failures through the generation of events (e.g., alarms) and activation of protective mechanisms when the monitored system function enters a faulty state. The safety monitoring functions can be implemented by hardware, software, or a combination of both. From the safety point of view, the safety monitor implements a safety barrier that will inhibit the failure of a software component from propagating throughout the system and adversely affecting its safety. Therefore, through the safety monitoring technique, the DAL level assigned to a software component will be derived from the severity of the consequence of the loss of the system function associated to that component. From a "schedulability" point of view, monitors are commonly used in safety-critical operating systems for the monitoring of the time budgets assigned to each application (or task). In case an application exceeds its time budget, an event is raised which is dealt with at the application level, i.e., each system may take different measures to compensate for those violations. In DAL-B systems for instance, the system could simply provide an indication for the user (a human or another system) that the integrity of the system has been compromised. This can be the case of aeronautic navigation systems, where several redundant instruments are available to aid performing the same navigation functions. This means that in case the integrity of a certain system has been compromised, it is still possible to use the readings of another instrument that performs identical functions.

DO-178C describes three important attributes that should be considered when designing the safety monitor. The first attribute is related to the monitor DAL assignment. The safety monitoring software inherits the DAL of the highest failure severity category associated with the monitored function (similarly to the IEC61508). The second attribute is aimed at ensuring that the monitors are designed and implemented in such a way that it will detect the intended faults under all necessary conditions (otherwise it cannot be trusted and thus becomes useless). In order to ensure that all fault conditions are identified, an assessment of the system faults needs to be performed to ensure that the monitoring and the monitored functions. The monitor and the protective mechanisms triggered by the events generated by the monitoring function should not be affected by the same failure causing the failure condition it is supposed to monitor. For instance, a monitor that is supposed to detect non-respected timing properties of

software components (e.g., due to starvation), cannot be subject to the same source of blocking as the monitored tasks. In this case, the monitor and the monitored tasks should for example be associated to different partitions.

#### 4.2 The IEC61508

The IEC61508 (2010) is a generic safety standard widely used throughout the industry. It serves as a common base for domain specific standards such as the ISO26262 (2011) (automotive), or EN 50128 (2009) (railway). IEC61508 is composed of a series of eight volumes addressing the complete safety life-cycle activities for systems comprised of electrical/electronic/programmable electronic (E/E/PE) elements (including software) that are used to perform safety functions. This standard defines strict rules regarding the *isolation* and *independence* between safety related and non-safety related functions. For instance:

"Where the software is to implement both safety and non-safety functions, then all of the software shall be treated as safety-related, unless adequate design measures ensure that the failures of non-safety functions cannot adversely affect safety functions." [Sect. 7.4.2.8 of IEC61508-3].

"Where the software is to implement safety functions of different safety integrity levels, then all of the software shall be treated as belonging to the highest safety integrity level, unless adequate independence between the safety functions of the different safety integrity levels can be shown in the design. It shall be demonstrated either (1) that independence is achieved by both in the spatial and temporal domains, or (2) that any violation of independence is controlled. The justification for independence shall be documented." [Sect. 7.4.2.9 of IEC61508-3].

Under IEC61508, several safety-related software design techniques and measures are presented as detailed below.

#### 4.2.1 Partitioning

Partitioning is a technique that allows isolating software components from each other. This isolation is essential for critical systems as it allows the containment of faults, as well as the reduction of the software V&V effort. Typically, there are two approaches to achieve partitioning between software components. The first approach is to *physically* segregate the components by allocating unique hardware resources to each component (i.e., only one software component is executed on each hardware component composing the system). The second approach is to *virtually* separate the components by establishing partitioned hardware provisions that allow multiple software components to run on the same hardware platform.

Annex F of IEC61508-3 provides further recommendations on techniques for achieving non-interference between software elements on a single computer. In this context, the term "independence of execution" is used, meaning that applications should not interfere with each other's behaviour. This independence *shall* be achieved and demonstrated in both *spatial* and *temporal* domains. Spatial isolation means that one application shall not change data used by another application. Note that spatial

isolation is even more important considering the fact that the highest severity software failure modes are typically associated to data corruption (e.g., due to buffer overflows or memory violation). Temporal isolation on the other hand shall ensure that one application will not cause malfunction of another application by consuming too high processor execution time or by blocking a shared resource used by other applications, thus affecting its timing properties. In order to demonstrate the independence of execution, an analysis of the proposed design is performed to determine the causes of execution interference in both spatial and temporal domain through the application of the methodologies described in Sect. 2.

The standard explicitly recommends the following techniques for achieving and demonstrating spatial independence (Sect. F.4 of IEC61508-3):

- 1. hardware memory protection;

- 2. virtual memory space;

- 3. rigorous design, source code and possibly object code analysis; and

- 4. software protection of higher integrity applications.

Ideally, data should not be passed between applications of different criticalities. However, in practice, especially in MCS, there may be a need to exchange data between applications of different criticalities. Considering this, the system should ensure that higher SIL applications are able to verify the integrity of any data received from lower SIL applications. This can be achieved, for instance, through the use of unidirectional interfaces such as messages or pipes, rather than through shared memory.

With respect to temporal independence, the following techniques (intrinsically related to the choice of scheduling policy) are mentioned by the standard (Sect. F.5 of IEC61508-3):

- 1. Deterministic scheduling methods such as cyclic scheduling and time triggered architectures;

- 2. Strict priority based scheduling by real-time executive (with mechanism to avoid priority inversion);

- Time fences that terminate the execution of an application in case it exceeds its time budget;

- 4. Time slicing, which ensures that no process can be starved of CPU time.

However, the resource sharing protocol is also important when sharing resources between applications, because the design shall ensure that the applications will not malfunction due to a locked resource. Therefore, it is essential that the time required to access a shared resource is taken into consideration when performing the timing analysis of the system.

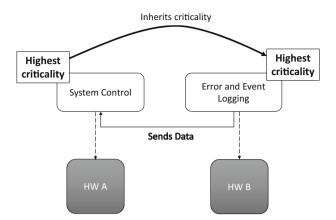

Note that the software functions used to provide spatial and/or temporal independence (e.g operating system, real-time executive) shall be allocated the *highest criticality* of the applications running on top of them (Sect. F.6 of IEC61508-3), since such software represents a potential common cause of failure of the independent elements. The diverse monitor (Sect. C.3.4 of IEC61508-7) is an architectural design technique that allows the protection against faults in software, preventing the system from entering an unsafe state. It is an external monitor, running in an independent hardware, which continuously monitors the main application. In the occurrence of a fault, the monitor will trigger an event (e.g., fire an alarm) so that a corrective measure can be activated, e.g., through a restart of the monitored application or through a human operator action. Typically, the utilization of a monitor allows to reduce the criticality of the monitored application. Indeed, following the FMEA analysis of the main application (see Sect. 2), the monitor would appear as a compensating provision that would prevent the failure from propagating throughout the system, thus reducing the criticality of the monitored application. However, in this case it can be considered that the monitor "inherits" the criticality of the monitored application, because if the monitor fails, there is typically no compensating provision to compensate for that failure. Therefore, the monitor is assigned a criticality derived from the highest severity failure modes of the monitored applications. In short, if the monitor can be certified at the highest criticality level, then the criticality level of the monitored component can be reduced under the condition that an effective corrective measure is available.

# 4.2.3 Dynamic reconfiguration

Another architectural design technique is the dynamic reconfiguration of the system (Sect. C.3.10 of IEC61508-7), whose objective is to maintain the system functions operational despite an internal fault. This concept is more commonly applied to the recovery from hardware faults, but it can also be applied to software, if the logical architecture of the system can be mapped onto a subset of the available resources, e.g., through "run-time redundancy" to allow a software re-try or through redundant data, which can reduce the severity of the consequence of an isolated failure.

# 4.2.4 Graceful degradation

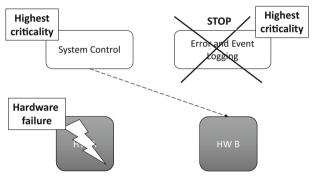

Graceful degradation is a technique aimed at maintaining the more important system functions available, despite failures, by dropping the less important system functions. According to the IEC61508-7, Sect. C.3.8:

"This technique gives priorities to the various system functions to be carried out by the system. The design ensures that if there is insufficient resources to carry out all the system functions, the higher priority functions are carried out in preference to the lower ones. For example, error and event logging functions may be lower priority than system control functions, in which case system control would continue if the hardware associated with error logging were to fail. Further, should the system control hardware fail, but not the error logging hardware, then the error logging hardware would take over the control function. This is predominantly applied to hardware but is applicable to the total system including software. It must be taken into account from the topmost design phase." As it will be further discussed in Sect. 6, most of the academic works on mixedcriticality scheduling claim to implement a graceful degradation strategy. To help understand the discussion that we will have in Sect. 6 about that claim, note already a few details of the quoted example:

- 1. The illustrative example involves a *high priority* function and a *low priority* function (i.e., it does not refer to criticality but priority).

- 2. The high priority task continues to run if the low priority task fails (i.e., a failure of a low priority task does not impact on the execution of a high priority task).

- 3. The hardware dedicated to the low priority function is used to execute the high priority task if the hardware of the high priority task comes to fail, thus stopping the execution of the low priority task.

- 4. The example assumes a hardware failure, which leaves the system with not enough hardware resource to serve all the software functions.

Note also that this is the only example given in the IEC61508 standard to describe the graceful degradation concept.

# 4.2.5 Performance modelling

Performance modelling (Sect. C.5.20 of IEC61508-7) ensures that the system operational capacity is sufficient to meet the specified throughput and response time requirements, considering any constraint on the use of system resources. The system processes and their interactions are modelled, including their demanded resources (e.g. CPU time) under average and worst-case conditions. Performance properties such as worst-case throughput and response times of the individual system functions are then calculated. To avoid the risk of resource starvation, the systems are often designed to use only some fraction of the total available resources (e.g. 50%, as explained in Sect. C.5.20 of IEC61508-7).

# 4.2.6 Response timing and memory constraints

It consists in determining the temporal and memory demands under average and worstcase conditions to ensure that the system requirements will be met (Sect. C.5.22 of IEC61508-7). One of the methods to obtain these estimates is through prototyping and benchmarking of time critical systems. In terms of schedulability analysis, this is the usual analysis that needs to be performed on MCS to ensure that all safetycritical system functions will successfully meet their deadlines under the given system constraints.

# 4.3 The ISO26262

ISO26262 is an adaptation of IEC61508 addressing the specific needs of the automotive sector. Therefore, everything discussed in the two previous subsections is also applicable to this standard. For instance, software partitioning aspects are addressed in Sect. 7.4.11 and in Annex D of ISO26262-6. Mechanisms for error detection at the software architectural level (including monitoring techniques) are listed in Table 4 of ISO26262-6. Several techniques for temporal and logical program sequence monitoring at the hardware level are also presented in Table D.10 of ISO26262-5.

From a shared resource viewpoint, if software partitioning techniques are to be applied, the resources shared between the partitions must be used in such a way that the software components running on the different partitions do not interfere with each other.

At the software architectural design level, the standard establishes that an upper estimation of required resources for the embedded software shall be made, which includes the execution time, the storage space (e.g. RAM for stacks and heaps) and the communication resources.

Annex D of ISO26262-6 (ISO26262 2011) also provides some common examples of timing and execution faults that can cause interference between software elements of different partitions and must therefore be assessed before certifying the system: blocking of execution, deadlocks, livelocks, incorrect allocation of execution time and/or incorrect synchronization between software elements. To prevent or mitigate these faults, some mechanisms are also referred such as: cyclic execution scheduling; fixed priority based scheduling; time triggered scheduling; monitoring of processor execution time; program sequence monitoring, and arrival rate monitoring. These important aspects must be considered when designing a real-time scheduling algorithm and/or a resource sharing protocol for MCS.

#### 4.4 Final remarks

In the previous subsections, we have presented a summary of several requirements from industrial standards that must be considered in the design of MCS. Those can be transversally applied to several domains of application (e.g. aerospace, automotive, railway). Although the presented safety-related industrial standards do not explicitly specify requirements for MCS, they do specify stringent requirements that must be met to ensure the *safety* of the system, especially in terms of isolation and independence between applications running on the same platform. Notwithstanding, the irreversible and inevitable appearance of multi-core hardware platforms in the industry introduces several additional challenges in terms of scheduling and resources sharing, which makes the isolation and independence of the mixed-criticality applications even more complex (and even more imperative). The requirements presented are clear in what concerns the isolation and independence of applications, even when they share common resources. Therefore, when designing a scheduling algorithm and/or resource sharing protocol that is intended to be compliant with such standards, it is necessary to provide evidences that the isolation between components is sufficient to avoid failure propagation between them. To address these challenges, several techniques have also been described that can be applied to the design of such systems, which can support the generation of the evidences required by the certification authorities.

#### 5 Industry solutions for mixed-criticality systems

After presenting in the previous section the summary of relevant requirements from safety-related standards for the design of MCS, we present two examples of industry solutions (ARINC-653 and AUTOSAR) that meet the isolation and independence requirements established by the previously presented industrial standards. As explained by Burns and Davis (2013), most avionics and automotive complex embedded systems are evolving to mixed-criticality systems, mainly due to increasingly demanding non-functional requirements related to cost, space, weight, heat dissipation and power consumption. ARINC-653 and AUTOSAR provide the basic platform for supporting MCS in avionics and automotive domains, respectively. However, the implementation of MCS solutions based on ARINC-653 and AUTOSAR, i.e., solutions that can satisfy the stringent partitioning requirements, but still allowing for efficient sharing of resources among the partitions is still a problem not fully solved by the industry by the time this paper is being written. As explained by Burns and Davis (2013), problems such as modelling and verification, and system problems related to the development of necessary hardware and software run-time controls are still currently being addressed. Therefore, with the goal of contributing to the research aimed at the resolution of those issues, we present next the key aspects of ARINC-653 and AUTOSAR that are relevant for the development of MCS.

#### 5.1 ARINC-653

ARINC-653 specifies the baseline operating environment for application software running on an Integrated Modular Avionics (IMA) (Watkins and Walter 2007; Diniz and Rufino 2005) platform or in traditional federated architectures developed according to ARINC 700 avionics standards (ARINC 2015).

The purpose of an IMA system is to support the execution of one or more avionics applications independently. Each application may have completely different requirements and thus be associated different DALs (i.e., criticalities). This separation is achieved through the partitioning technique, which provides the functional separation of the applications (mainly to inhibit failure propagation), as well as the facilitation of the V&V activities. A partition is basically an environment running a program, comprising its own data, context, configuration attributes, etc.

The primary objective of ARINC-653 is to define a general-purpose interface between the avionics application software and the operating system (OS) running on a avionics computer. This interface is known as the APEX (APlication/EXecutive). The APEX defines the interfaces that allow the applications software to control the OS scheduling, communication and status information functions. The key objectives of the APEX interface are portability, reusability, modularity and integration of software of multiple criticalities, i.e. it supports the co-location of software applications of different levels of criticality. However, it is important to note that the APEX interface merely defines the services that the OS needs to provide. It is up to the OS provider to implement those services.

Under ARINC-653, it is required that the hardware offers the following functionalities to the OS: ability to restrict memory spaces, processing time and access to I/O for each individual partition.

Although industrial solutions such as ARINC-653 exist, most of them were initially intended for single-core platforms and must now be extended to multi-core.

The following subsections briefly describe some key functionalities specified by ARINC-653 that are pertinent to this work.

#### 5.1.1 Partition management

The partitioning concept is central to the ARINC-653 philosophy, whereby the programs resident on the partitions are partitioned with respect to space (memory partitioning) and time (temporal partitioning). The partitioned system has to be robust enough to support applications of different criticality levels to execute in the same core platform, without affecting each other, both spatially and temporally.

The scheduling of partitions shall be strictly deterministic over time. Based on the configuration of the partitions, time windows are assigned to each partition which are then activated on a time-based schedule. The schedule is fixed for a particular configuration. Partitions are scheduled on a fixed, cyclic basis. This provides a deterministic scheduling methodology whereby partitions are assigned a fixed amount of CPU time. This ensures that each partition will have uninterrupted access to common resources during its assigned period. The scheduling configuration is done by the system integrator only and thus cannot be modified during operation. The memory areas allocated to each partition are predefined. Access outside each partition's assigned memory area is forbidden.

#### 5.1.2 Process management

In ARINC-653, the term "process" is used to designate each "task" comprised within a partition. Still, the term task is more commonly adopted within the real-time community and it is the term chosen to be used in this paper.

Considering the IMA concept, within each partition, the scheduling model defines the tasks as the scheduling units. One or more tasks can operate concurrently to provide the aeronautic functions required by the partition. A fixed priority is assigned to each task. A task can be preempted at any time by another with higher priority. The tasks may be periodic or sporadic and certain scheduling capabilities are required by the OS to accurately control the tasks execution in order to meet the application timing requirements. These tasks interact with the OS through the APEX interfaces and the OS is responsible to arbitrate the tasks access to the CPU. The occurrence of a fault may trigger an action to either initialize or terminate a task. Therefore, a method is required to safely synchronize the access to the system's mutually exclusive resources. The partition code executes in *user mode* only, i.e. no privileged instructions are allowed. It is also important to highlight that the above concepts are applicable to the tasks inside a partition, i.e., tasks that have the same criticality level. Hence, the decision to terminate a task in case of misbehaviour is not linked with its criticality, but rather with the application requirements.

# 5.1.3 Memory allocation

The partitions and their associated memory spaces are defined during system configuration, i.e. offline. The APEX interface does not offer memory allocation services. The exchange of information between tasks pertaining to different partitions can be done through buffers, which are also declared at the system configuration.

# 5.1.4 Intrapartition communication

Intrapartition communication is performed by means of buffers, blackboards, semaphores, and events. Buffers and blackboards are used for general inter-process communication, whereas semaphores and events are used for inter-process synchronization. Buffers and blackboards allow processes to communicate by exchanging messages that are directed to the respective buffers and blackboards associated with the destination processes. The memory space required to manage buffers and blackboards and to store messages is allocated for the partitions memory and is configured at design time. Buffers store multiple messages in message queues, either in FIFO or priority order. Blackboards on the other hand do not allow message queueing. Messages written to a blackboard remain there until they are either cleared or overwritten by a new instance of the message.

# 5.1.5 Intepartition communication

Interpartition communication is conducted via the exchange of *messages* through a *channel*. A message is defined as a continuous block of data of finite length. The channels define a logical link between a source partition and one or more destination partitions. The partitions can access the channels via defined access points designated as ports. The ports provide the required resources that allow a partition to send and receive messages over a specific channel. It is important to note that the destination of a message is always a partition, and not a process within a partition. As for intrapartition communications, interpartition communication is also performed with queues and blackboards.

# 5.1.6 Time management

The OS provides time slicing for partition scheduling, deadline, periodicity, and delays for task scheduling. Timeouts for intrapartition and interpartition communication are also provided in order to manage time. Time is unique and independent of partition execution. A time capacity is associated with each task that ensures that its processing requirements are met. When a task starts, its deadline is set to the value of the current time plus an execution time capacity.

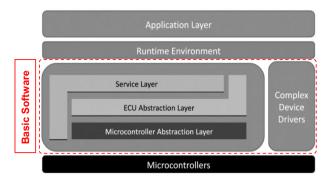

Fig. 2 AUTOSAR architectural overview (AUTOSAR 2011)

# **5.2 AUTOSAR**

AUTOSAR appears as a response of the automotive industry OEMs (Original Equipment Manufacturers) to the increase of complexity on vehicle applications. It is a standardized and open software architecture that can be used for the diverse in-vehicle systems without compromising the quality and with cost-efficiency. The software that implements the automotive functionality is mainly encapsulated in software components. The standardized functional interfaces (with different layers) of those components are a central element to support scalability and transferability of automotive functions across electronic control units of different vehicle platforms. AUTOSAR achieves the standardization of functional interfaces across manufacturers and suppliers and also the standardization of interfaces between different software layers. Hardware abstraction layers are present upon these, besides the software specific ones.

The standard scope includes all vehicle domains, and serves as a platform upon which vehicle applications can be implemented. This process aims at minimizing the barriers between the functional domain and the mapping of functions and functional networks, almost independently of the associated hardware. The illustration presented in Fig. 2 describes an AUTOSAR architectural overview.

By looking at Fig. 2 bottom-up, the following layers are identified:

Basic Software (BSW): The standardized software layer that provides the services to the AUTOSAR application software components (functional part), including the communication with the hardware. The functional part needs the basic software layer to run, but the BSW layer does not perform any functional job itself. The BSW is composed of the following sub-layers: Complex Device Drivers (CDD), hardware abstraction (ECU<sup>4</sup> and Microcontroller) and AUTOSAR Services. The CDD is a loosely coupled container, where specific software implementations can be placed. The main goal of the CDD is to provide support for complex sensors and actuators that have special functional and timing requirements. It might also be used to encapsulate legacy functionality of a non-AUTOSAR system (AUTOSAR 2015). The Microcontroller abstraction layer (MCAL) provides a standard inter-

<sup>&</sup>lt;sup>4</sup> ECU: Electronic Control Unit

face to the components of the BSW, which avoids direct access to microcontroller registers from higher-level software (AUTOSAR 2011). The ECU abstraction provides the software interface to the specific ECU electrical interfaces, thus removing all the higher-level software dependencies from the underlying hardware. The Services sub-layer is split into three main services: general services (e.g. diagnostic protocols and memory management), communications (e.g. CAN), operating system services (e.g. priority-based scheduling).

- Runtime Environment (RTE): RTE implements the communication functions for inter- and intra-ECU information exchange. It provides communication abstraction to the software components attached to it at the application layer, which is independent from whether inter-ECU communication channels (e.g. CAN) are used or communications are intra-ECU. RTEs are ECU specific and need to be tailored according to the communication requirements of the software components running on top of them. Note that in the AUTOSAR concept, the RTE is the concretization of the *Virtual Functional Bus (VFB)*. The VFB is an abstraction layer that allows the communication between different AUTOSAR Software Components and its environment (e.g. hardware driver, OS, services, etc.) to be specified independently from any underlying hardware (e.g. a communication system). The advantage of this approach is that it enables the virtual integration of different automotive software components very early in the design process.

- Software Component (SWC): the application layer is composed of interconnected "AUTOSAR Software Components". The AUTOSAR SWCs are atomic pieces of software that implement part of an application, are independent of the infrastructure, and can be mapped on an ECU. Each Software Component within an ECU encapsulates a distinct part of the overall application functionality. SWCs expose well-defined interfaces, described and standardized within AUTOSAR.

The AUTOSAR OS standard specifies a fixed priority preemptive RTOS with support for multi-core. Some aspects of the AUTOSAR OS that are relevant to the support of mixed-criticality are discussed in the following subsections.

# 5.2.1 Time partitioning

AUTOSAR requirement SRS\_Os\_11008 (AUTOSAR 2013) specifies that the OS shall not allow a timing fault in any OS-Application to propagate to other applications running on the same processor. A timing fault of a task or interrupt service routing (ISR) occurs when: (i) the specified execution time is violated or (ii) the specified arrival rate is violated. To ensure that a task or ISR meets its deadline in a fixed priority preemptive operating system like AUTOSAR OS, the following protections are necessary:

- Prevention of timing errors from the execution time of Task/ISRs in the system by using *execution time protection* to guarantee a statically configured upper bound, called the Execution Budget;

- Prevention of timing errors from the blocking time that tasks/ISRs suffers from lower priority tasks/ISRs locking shared resources or disabling interrupts by using

*locking time protection* to guarantee a statically configured upper bound, called the Lock Budget;

Prevention of timing errors from the inter-arrival rate of task/ISRs in the system by using inter-arrival time protection to guarantee a statically configured lower bound, called the Time Frame;

#### 5.2.2 Space partitioning

AUTOSAR requirement SRS\_Os\_11005 (AUTOSAR 2013) specifies that the OS shall provide the ability of partitioning OS-Applications with respect to memory and prevent an OS-Application from modifying the memory of other OS-Applications. However, memory protection under AUTOSAR is only possible on processors that provide hardware support for memory protection. The memory protection scheme is based on the (data, code and stack) sections of the executable program, as described next:

- Stack protection: an OS-Application comprises a number of tasks and ISRs. Memory protection for the stacks of tasks and ISRs is important because it:

- provides a more immediate detection of stack overflow and underflow for the task or ISR than can be achieved with stack monitoring;

- provides protection between constituent parts of an OS-Application, for example to satisfy some safety constraints;

- Data protection: OS-Applications can have private data sections and tasks/ISRs can have private data sections. OS-Application's private data sections are shared by all tasks/ISRs belonging to that OS-Application;

- Code protection: code sections are either private to an OS-Application or can be shared between all OS-Applications (to use shared libraries). In the case where code protection is not used, executing incorrect code will eventually result in a memory, timing, or service violation.

#### 5.2.3 Communications between applications

Since AUTOSAR requires that OS-Applications be protected against each other, a mechanism needs to be provided to transport data between those applications. AUTOSAR offers a communication mechanism to transfer data between OS-Applications: the Inter OS-Application Communicator (IOC).

The IOC is part of the operating system and is responsible for the communication between OS-Applications and in particular for the communication crossing core or memory protection boundaries. The IOC is a third type of communication, in addition to: intra OS-Application communication (always handled within the RTE) and inter ECU communication [already available via well defined interfaces to the communication stack (COM)]. The IOC offers communication of data to another core or between memory protected partitions with guarantee of data consistency. The IOC provides communication buffers, queues, and protected access functions/macros to these buffers that can be used from any pre-configured partitions concurrently.

# 5.3 Final remarks

After having analysed the key aspects of the industry solutions for implementing mixed-criticality systems, there are some important aspects that need to be highlighted. Although the ARINC-653 and AUTOSAR approaches have some commonalities, these standards propose very different techniques to solve the issues of independence and isolation between applications. In ARINC-653 this goal is achieved through hierarchical scheduling, where partitions are scheduled using a table driven approach, i.e., no changes can be made to the schedule during run-time, hence resulting in a system with reduced flexibility. This scheduling policy renders the isolation extremely robust against any timing fault. However, it also involves a complex configuration phase where partitions must be dimensioned and the partition schedule compiled. System integrators must consider the timing constraints of each independent task along with the interactions between all the different partitions, I/O devices and other shared resources. AUTOSAR on the other hand proposes a more flexible approach, which does not specify a specific scheduling policy, and is thus more open (or less conservative); note, however, that AUTOSAR still specifies timing protection requirements that must be provided to prevent a timing fault in any OS-Application to propagate to a different application resident in the same processor. ARINC-653 and AUTOSAR have similar requirements with respect to spatial partitioning and in both cases, the communication between partitions/applications must be made through a protective layer, i.e., a mechanism to transport data between applications. ARINC-653 uses messages and channels, and AUTOSAR uses the IOC.

# 6 The theoretical MC model and its certification concerns

In the previous sections we have presented the main design principles and requirements that drive the development of industrial MCS. We now move the focus of the paper to the academic work. We will discuss one of the most prominent model adopted in the state-of-the-art and some common misconceptions.

# 6.1 The state-of-the-art in academy

These last years, the real-time research community has been extremely active in the domain of MCS. Almost 200 papers treating of the scheduling of MCS have been referenced in Burns and Davis (2013), and tens of related papers are still published every year. It would therefore be unrealistic to review and analyse here the whole state-of-the-art on real-time scheduling of MCS. Instead, this section evaluates the key concepts and approaches commonly encountered in real-time scheduling models and algorithms against the recommendations and requirements found in the safety-related industrial standards that were presented in the previous sections.

Most of the works about MCS published by the real-time scheduling research community are based on a model proposed by Vestal (2007). Therefore, we will mainly focus on that specific model and its related work. Yet, the discussion proposed in the

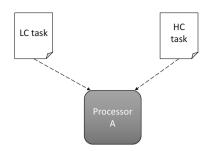

rest of this chapter is quite generic and most of the remarks made are thus valid for other academic MC models introduced during the last decade. The Vestal model assumes that the system has several modes of execution, say modes  $1, 2, \ldots, L$ . The application system is a set of real-time tasks, where each task  $\tau_i$  is characterized by a period and a deadline (as in the usual real-time task model), an assurance level  $\ell_i$  and a set of worstcase execution time (WCET) estimates  $\{C_{i,1}, C_{i,2}, \ldots, C_{i,\ell_i}\}$ , under the assumption that  $C_{i,1} \leq C_{i,2} \leq \cdots \leq C_{i,\ell_i}$ . The different WCET estimates are meant to model estimations of the WCET at different assurance levels. The worst time observed during tests of normal operational scenarios might be used as  $C_{i,1}$  whereas at each higher assurance level the subsequent estimates  $C_{i,2}, \ldots, C_{i,\ell_i}$  are assumed to be obtained by more conservative WCET analysis techniques or by considering safety margins imposed by certification authorities. Vestal initially studied the schedulability of the system under such assumptions and proposed a task priority assignment algorithm optimising the overall schedulability. In later works, solutions started to be proposed in order to improve the schedulability of higher criticality tasks over the lower criticality ones. Those solutions usually rely on variations of the following scheme (Baruah et al. 2011). The system starts its execution in mode 1 and all the tasks are scheduled to execute on the core [s]. Then at runtime, if the system is running in mode k then each time the execution budget  $C_{i,k}$  of a task  $\tau_i$  is overshot, the system switches to mode k + 1. It results from this transition from mode k to mode k + 1 that all the tasks of criticality not greater than k (i.e.,  $\ell_i \geq k$ ) are suspended. Mechanisms have also been proposed to eventually re-activate the dropped tasks at some later points in time (Santy et al. 2013).

It must be noted that one of the derivatives/simplifications of this model is the Vestal's model with only two modes, usually referred to as LO and HI modes (which stand for Low- and High-criticality modes). Multiple variations of that scheduling scheme exist (please refer to Burns and Davis (2013) for a comprehensive survey); some for single-core, others for multi-core architectures. In the case of multi-core, both global and partitioned scheduling techniques have been studied. Solutions for fixed priority scheduling, earliest deadline first, and time-triggered scheduling have been proposed. Some works also propose to change the priorities or the periods of the tasks during a mode change rather than simply stopping the less critical ones. Note that we use Vestal's model to illustrate this section as most (not all) theoretical works in the state-of-the-art are based on similar assumptions. However, as mentioned in Burns and Davis (2013), more practical solutions such as the EMC2 framework (Chisholm et al. 2016; Kim et al. 2016; Chisholm et al. 2015) are also being developed in the context of academic research. Even if those works are not directly mentioned here, we believe that some of the concepts discussed in this section may be useful to back up choices made in those more applied researches.