# P-SCRATES

Parallel SOftware framework for time-CRitical mAny-core sysTEmS

#### Context

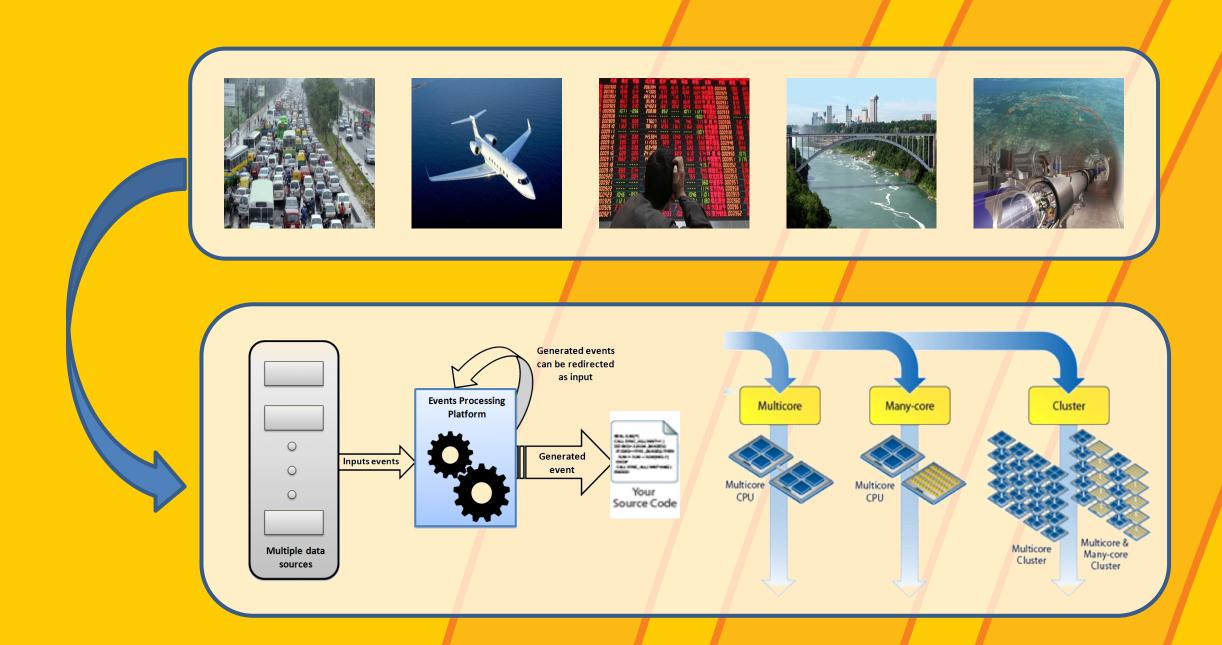

The prevalence of computing systems in our lives is so ubiquitous that it would not be far-fetched to state that we live in a cyber-physical world dominated by computer systems.

Applications demand more and more computational performance to process big amounts of data coming from real-time sensor information. This guarantee is vital for systems such as planes, cars, traffic management, business monitoring, e-trading, etc.

Processors are constantly required to become more and more powerful and reliable, while remaining affordable: the so called many-core processors have recently started to contain dozens or hundreds of cores, interconnected with complex networks on chip.

This paved the way for parallel computing: rather than processing the data sequentially, the cooperation of multiple processing elements allows systems to execute in parallel.

#### Goals

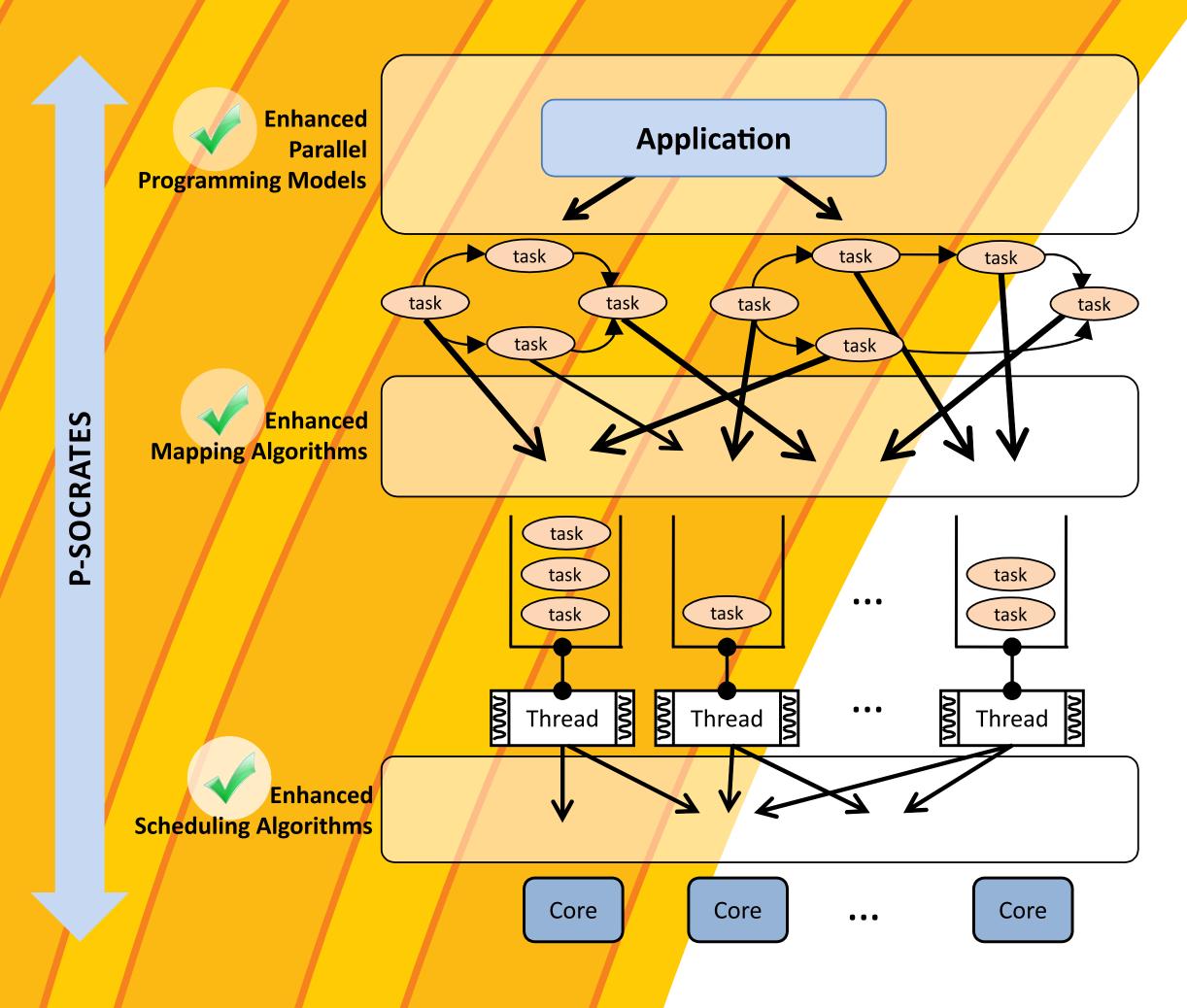

The aim of P-SOCRATES is to allow applications with high-performance and real-time requirements to fully exploit the performance opportunities brought by the most advanced many-core processors, whilst ensuring a predictable performance and maintaining (or even reducing) development costs of applications.

P-SOCRATES will develop a new generic design framework, from the conceptual design of the system functionality to its physical implementation.

Industrial companies will benefit from the project outcomes, allowing to exploit the capabilities of next-generation hardware platforms in a predictable way. Impacts are foreseen in the development of enabling technologies for both the high-performance and embedded computing domains.

From an applicative point of view, P-SOCRATES will represent a reference point for the implementation of workload-intensive applications with time-criticality requirements, enabling a more efficient smart society.

The computing technology developed in the project will allow a deeper understanding of many-core off-the-shelf systems, enabling new kinds of applications to be developed on top of these platforms.

### **Partners**

## Challenges

Parallelization brings many challenges: it affects the timing behaviour of systems as well as the way people think and the design computers: from the hardware architecture, through the operating system up to the design of the application.

Although many-core processors are promising candidates to improve responsiveness, timing guarantees become harder, as the behaviour of the system depends on interactions within the chip that are most of the time not known by the system designer.

Most of the optimization mechanisms buried deep inside the chip are geared only to increase performance and execution speed rather than providing predictable time behaviour.

Funded under

Seventh Framework Programme,

Advanced computing, embedded

and control systems

(ICT-2013.3.4)

Project reference: 611016

Total cost: 3.62M EUR

EU contribution: 2.76M EUR

Start Date: 2013-10-01

Duration: 36 months